# TECHNICAL MANUAL MAGNETIC TAPE SYSTEM MODEL 7371/7372/7374

October 1968

# LIST OF EFFECTIVE PAGES

Total number of pages is 266, as follows:

| Page No.       | Issue    | Page No. | Issue |

|----------------|----------|----------|-------|

| Title          | Original |          |       |

| A              | Original |          |       |

| i thru x       | Original |          |       |

| 1-1 thru 1-6   | Original |          |       |

| 2-1 thru 2-14  | Original |          |       |

| 3-1 thru 3-148 | Original |          |       |

| 4-1 thru 4-86  | Original |          |       |

### TABLE OF CONTENTS

| Section |              | Title                                                                                | Page |

|---------|--------------|--------------------------------------------------------------------------------------|------|

| I       | GENE         | RAL DESCRIPTION                                                                      | 1-1  |

|         | 1-1          | Introduction                                                                         | 1-1  |

|         | 1-2          | Scope of Manual                                                                      | 1-1  |

|         | 1-3          | Related Publications                                                                 | 1-1  |

|         | 1-4          | Purpose and Brief Description                                                        | 1-1  |

|         | 1-5          | Physical Description                                                                 | 1-1  |

|         | 1-6          | General                                                                              | 1-1  |

|         | 1-7          | Magnetic Tape Station                                                                | 1-1  |

|         | 1-8          | Transport Assembly                                                                   | 1-1  |

|         | 1-9          | Operator Control Panel                                                               | 1-3  |

|         | 1-10         | Vacuum System                                                                        | 1-3  |

|         | 1-11         | Positive Pressure System                                                             | 1-3  |

|         | 1-12         | Blower Shelf Assembly                                                                | 1 –3 |

|         | 1-13         | Relay Chassis Assembly                                                               | 1 -4 |

|         | 1-14         | Power Supplies                                                                       | 1 –4 |

|         | 1-15         | Power Distribution Chassis                                                           | 1 -4 |

|         | 1-16         | Transport Drive Electronics                                                          | 1 –4 |

|         | 1-1 <i>7</i> | Station Electronics                                                                  | 1 –4 |

|         | 1-18         | Magnetic Tape Controller                                                             | 1 –4 |

| -       | 1-19         | Functional Description                                                               | 1 –4 |

|         | 1-20         | Magnetic Tape Station                                                                | 1 –4 |

|         | 1-21         | Magnetic Tape Controller                                                             | 1 –4 |

|         | 1-22         | Tape Format                                                                          | 1 –4 |

|         | 1-23         | Specifications and Leading Particulars                                               | 1 –4 |

|         | 1-24         | General Requirements                                                                 | 1 -4 |

|         | 1-25         | Fuse and Lamp Complement                                                             | 1-6  |

| II      | OPERA        | TION AND PROGRAMMING                                                                 | 2-1  |

|         | 2-1          | Controls and Indicators                                                              | 2-1  |

|         | 2-2          | Operator Control Panel Switches                                                      | 2-1  |

|         | 2-3          | Auxiliary (Maintenance) Control Panel Switches · · · · · · · · · · · · · · · · · · · | 2-1  |

|         | 2-4          | Swinging Front Door Interlock Switch                                                 | 2-1  |

|         | 2-5          | Power Distribution Chassis Switches                                                  | 2-4  |

|         | 2-6          | Power Supply Switches and Fuses                                                      | 2-4  |

|         | 2-7          | Manually Operated Interlock Switches                                                 | 2-4  |

|         | 2-8          | Operating Instructions                                                               | 2-6  |

|         | 2-9          | Initial Turn-On Procedure                                                            | 2-6  |

|         | 2-10         | Tape Preparation                                                                     | 2-6  |

|         | 2-11         | Reflective Markers                                                                   | 2-6  |

|         | 2-12         | File Protect Ring                                                                    | 2-6  |

|         | 2-13         | Push-On, Pull-Off (POPO) Hub Assembly                                                | 2-6  |

|         | 2-14         | Loading the Transport                                                                | 2-7  |

|         | 2-15         | On-Line Operation                                                                    | 2-7  |

|         | 2-16         | Turnoff Procedure                                                                    | 2-7  |

|         | 2-17         | Programming                                                                          | 2-8  |

|         | 2-18         | Magnetic Tape System I/O Instructions and Responses                                  | 2-8  |

|         | 2-19         | Start Input/Output (SIO)                                                             | 2-8  |

|         | 2-20         | Halt Input/Output (HIO)                                                              | 2-9  |

|         | 2-21         | Test Input/Output (TIO)                                                              | 2-9  |

|         | 2-22         | Test Device (TDV)                                                                    | 2-10 |

| ection |            | Title                                      | Page |

|--------|------------|--------------------------------------------|------|

|        | 2-23       | Acknowledge Input/Output Interrupt (AIO)   | 2-10 |

|        | 2-24       | Magnetic Tape System Conditions            | 2-10 |

|        | 2-25       | Input/Output Address Recognition           | 2-11 |

|        | 2-26       | Station Operational                        | 2-11 |

|        | 2-27       | Station Ready                              | 2-11 |

|        | 2-28       | Controller Ready                           | 2-11 |

|        | 2-29       | Station Automatic                          | 2-11 |

|        | 2-30       | Magnetic Tape System Orders                | 2-11 |

|        | 2-31       | Order Codes                                | 2-11 |

|        | 2-32       | Order Descriptions                         | 2-11 |

|        | 2-33       | Termination of Order and Error Indications | 2-12 |

|        | 2-34       | Example of Control Line Programming        | 2-13 |

|        | 2-35       | Directive Sequencing                       | 2-13 |

|        | 2-36       | Program Execution                          | 2-13 |

|        | 2-37       | Control Line                               | 2-13 |

| III    | PRINC      | IPLES OF OPERATION                         | 3-1  |

|        | 3-1        | Introduction                               | 3-1  |

|        | 3-1        | General Information                        | 3-1  |

|        | 3-3        | Data Transfer Modes                        | 3-1  |

|        | 3-4        | Binary Mode                                | 3-1  |

|        | 3-4        | Binary Coded Decimal Mode                  | 3-1  |

|        | 3-6        | Packed Binary Mode                         | 3-1  |

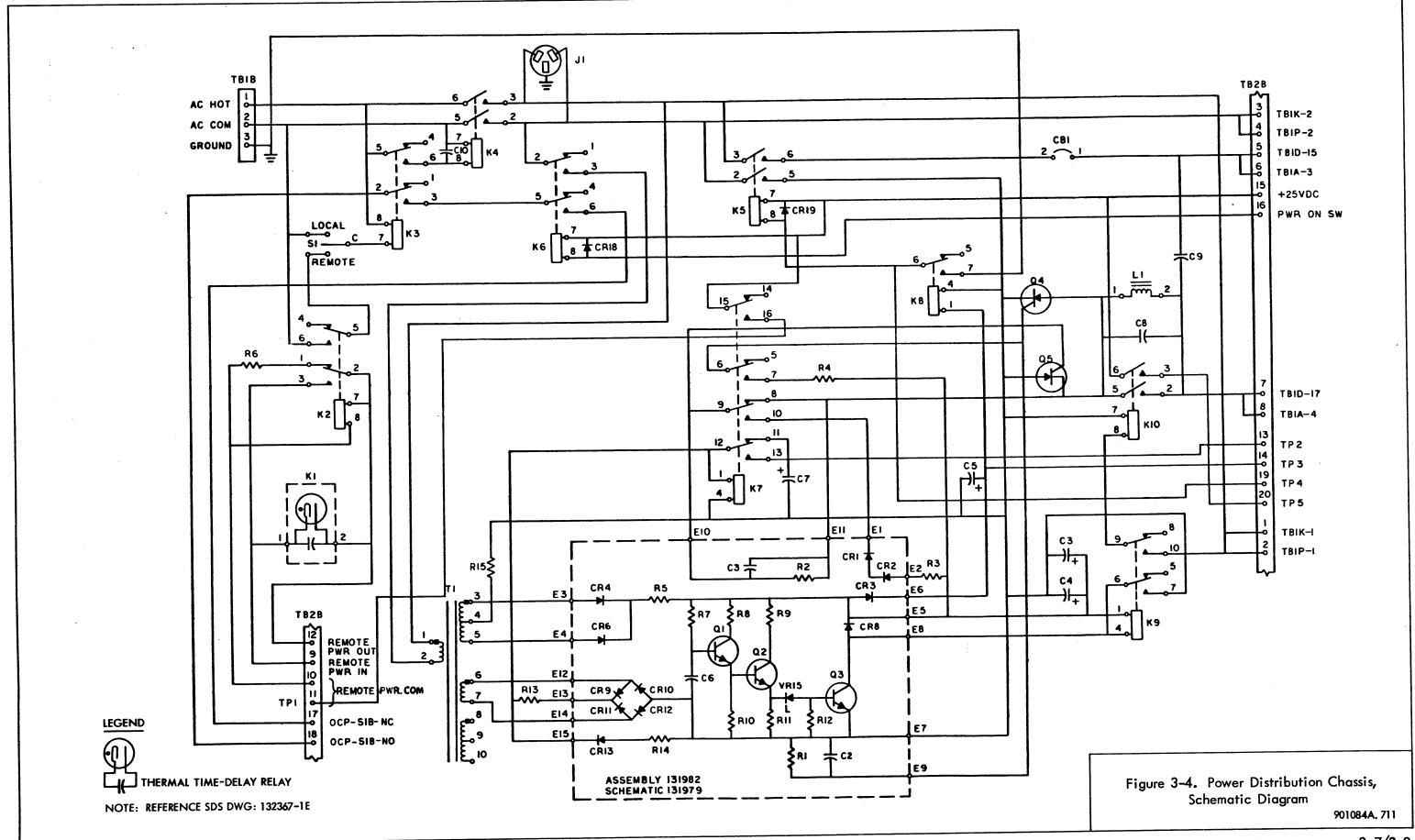

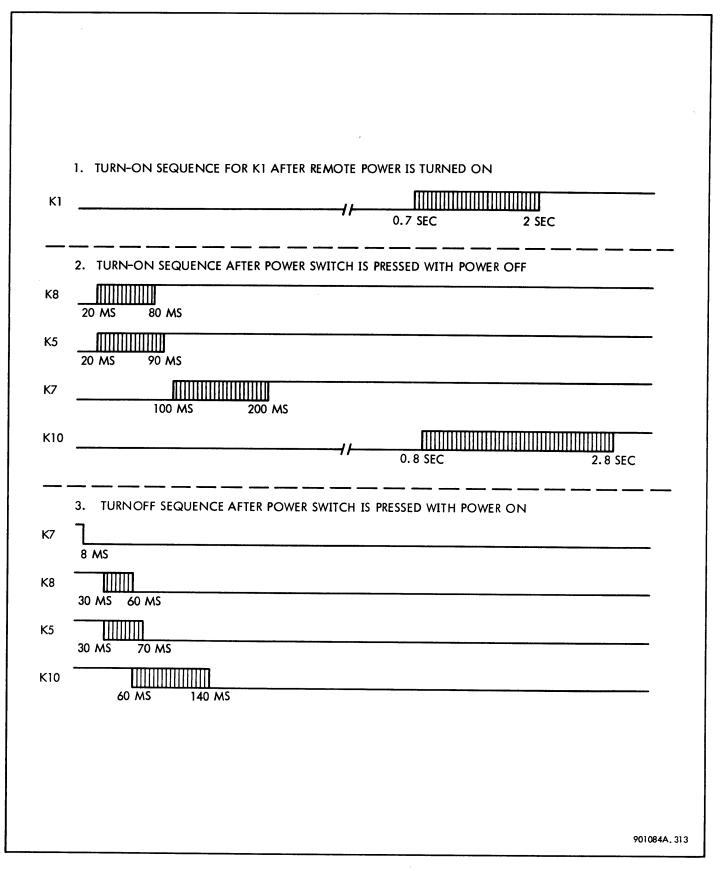

|        | 3-0<br>3-7 | Power Circuits                             | 3-4  |

|        | 3-8        | Primary Power                              | 3-4  |

|        | 3-9        | Power Distribution                         | 3-9  |

|        | 3-10       | Turn-On Sequence                           | 3-9  |

|        | 3-10       | Turnoff Sequence                           | 3-9  |

|        | 3-12       | Station                                    | 3-9  |

|        | 3-13       | Pneumatics                                 | 3-9  |

|        | 3-14       | Positive Pressure System                   | 3-12 |

|        | 3-15       | Vacuum System                              | 3-12 |

|        | 3-16       | Mechanics                                  | 3-14 |

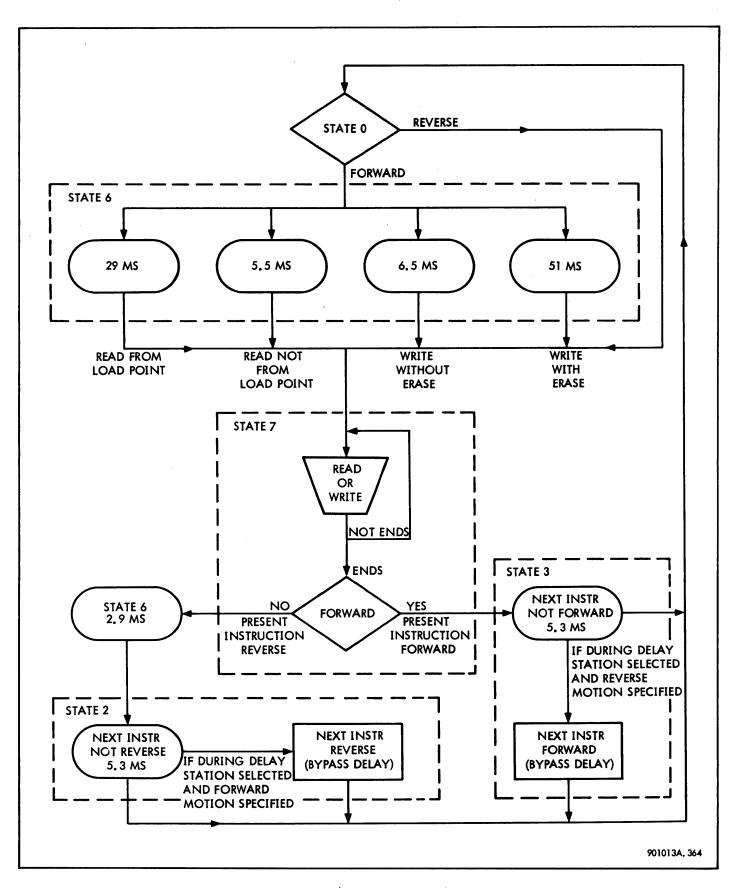

|        | 3-17       | Capstan Motion                             | 3-14 |

|        | 3-18       | Reel Motion                                | 3-23 |

|        | 3-19       | Fast Motion                                | 3-29 |

|        | 3-20       | Load Operation                             | 3-30 |

|        | 3-21       | Heads                                      | 3-33 |

|        | 3-22       | Read/Write Head                            | 3-34 |

|        | 3-23       | Erase Head                                 | 3-34 |

|        | 3-24       | Photosense Head                            | 3-34 |

|        | 3-25       | Motion Electronics                         | 3-34 |

|        | 3-26       | Delay Count Register                       | 3-34 |

|        | 3-27       | State Counter                              | 3-38 |

|        | 3-28       | Station Selection                          | 3-41 |

|        | 3-29       | Station Deselection                        | 3-41 |

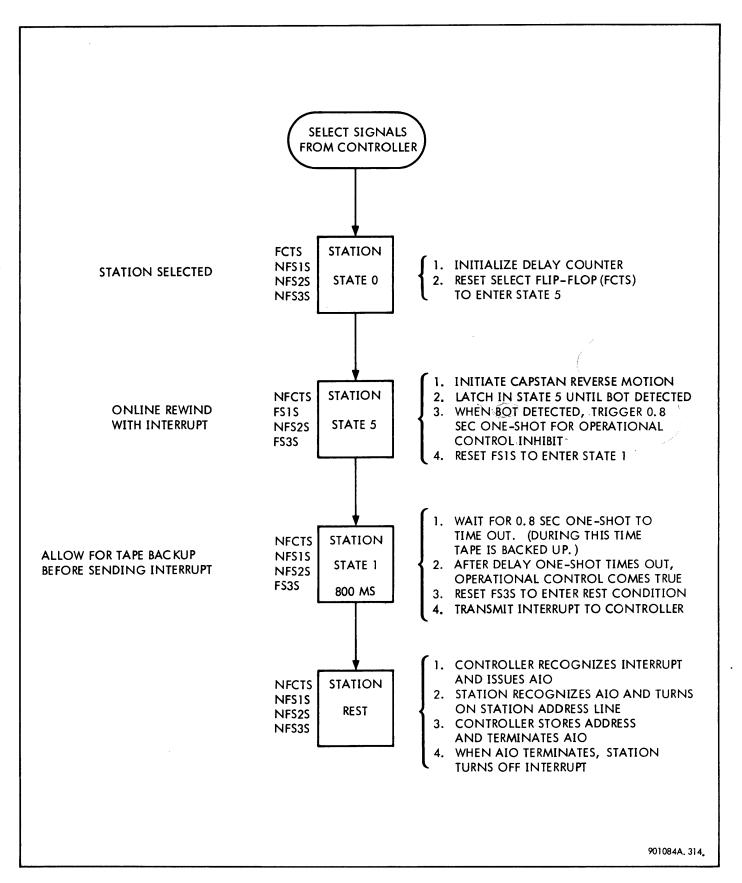

|        | 3-30       | Rewind Operation                           | 3-42 |

|        | 3-31       | Erase Operation                            | 3-45 |

|        | 3-32       | Spacing Operation                          | 3-46 |

|        | 3-33       | Controller                                 | 3-46 |

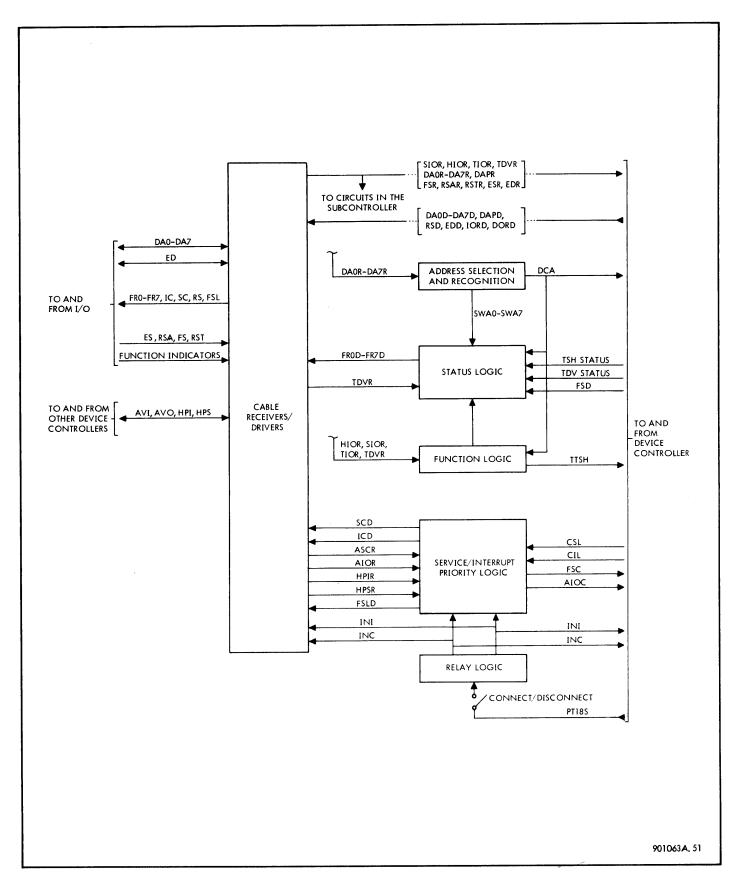

|        | 3-34       | Interface                                  | 3-47 |

|        | 3-35       | Data Path                                  | 3-49 |

|        | 3-36       | IOP-Controller Signals                     | 3-49 |

|        | 3-37       | Controller-Station Signals                 | 3-54 |

|        | 3-38       | Interface Disconnect                       | 3-55 |

| Section |              | Title                                                                   | Page          |

|---------|--------------|-------------------------------------------------------------------------|---------------|

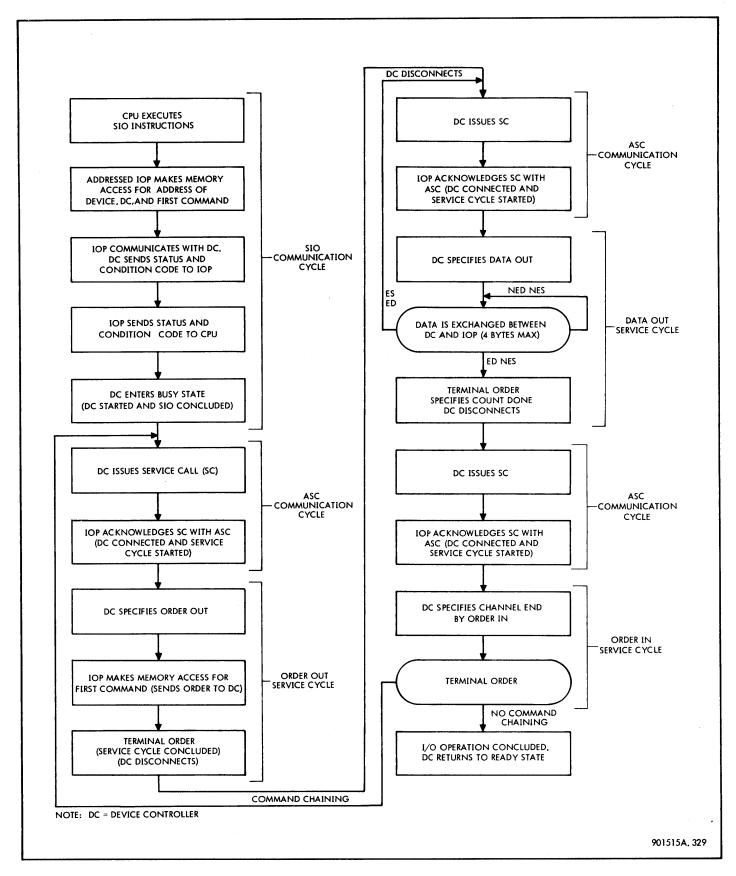

|         | 3-39         | Communication Cycles                                                    | 3-56          |

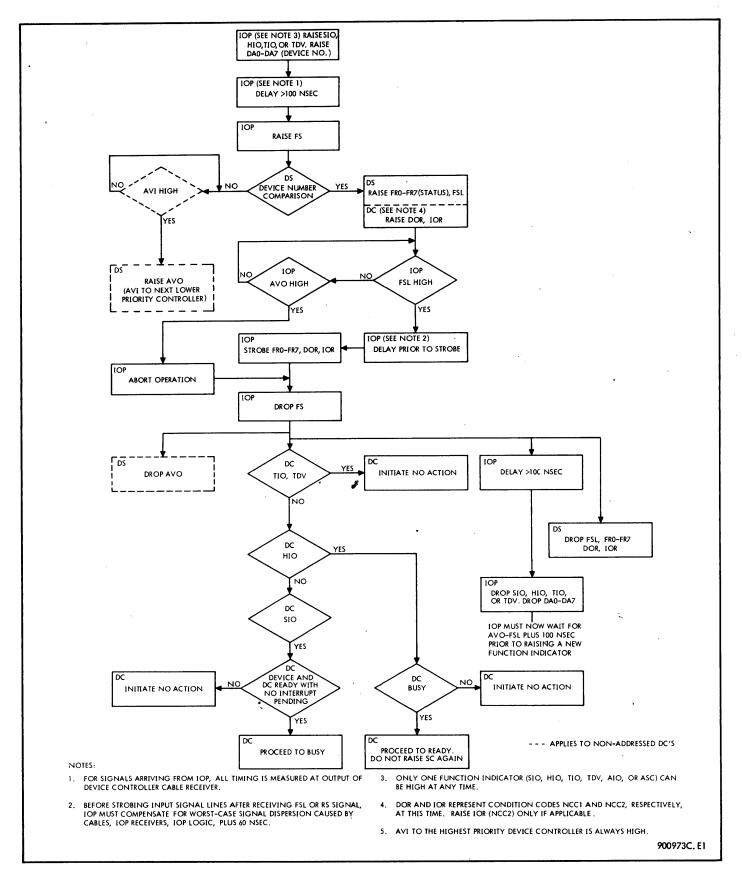

|         | 3-40         | Start Input/Output (SIO)                                                | 3-56          |

|         | 3-41         | Acknowledge Input/Output (AIO)                                          | 3-60          |

|         | 3-42         | Acknowledge Service Call (ASC)                                          | 3-62          |

|         | 3-43         | Service Cycles                                                          | 3-64          |

|         | 3-44         | Order Input                                                             | 3-64          |

|         | 3-45         | Order Output                                                            | 3-64          |

|         | 3-46         | Data Input and Data Output                                              | 3-64          |

|         | 3-47         | Terminal Order                                                          | 3-71          |

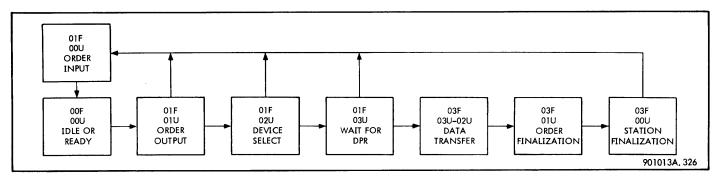

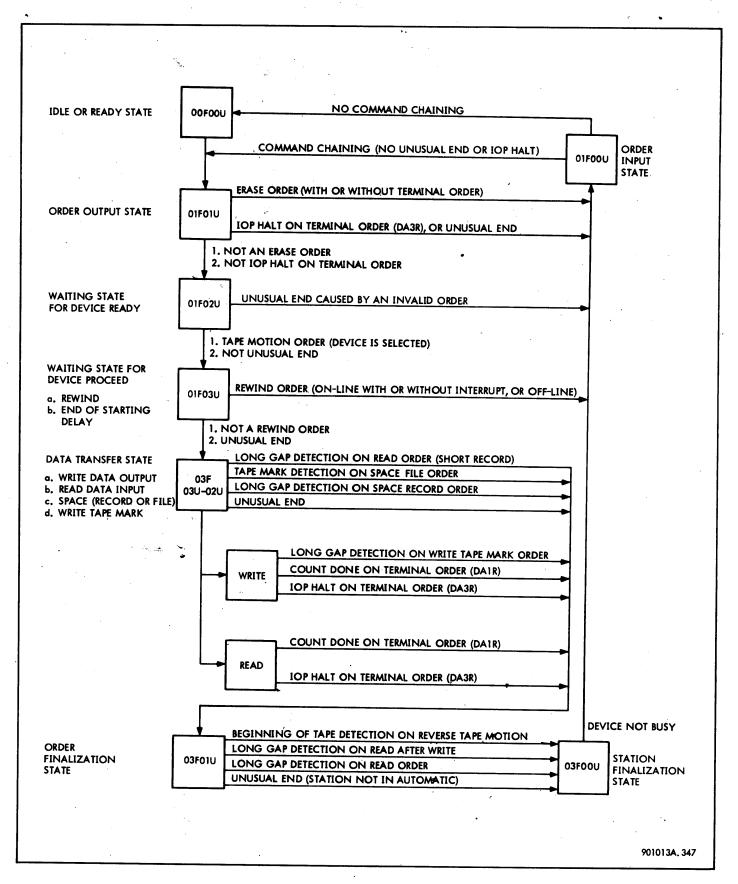

|         | 3-48         | States                                                                  | 3-71          |

|         | 3-49         | O0F00U, Idle or Ready                                                   | 3-71          |

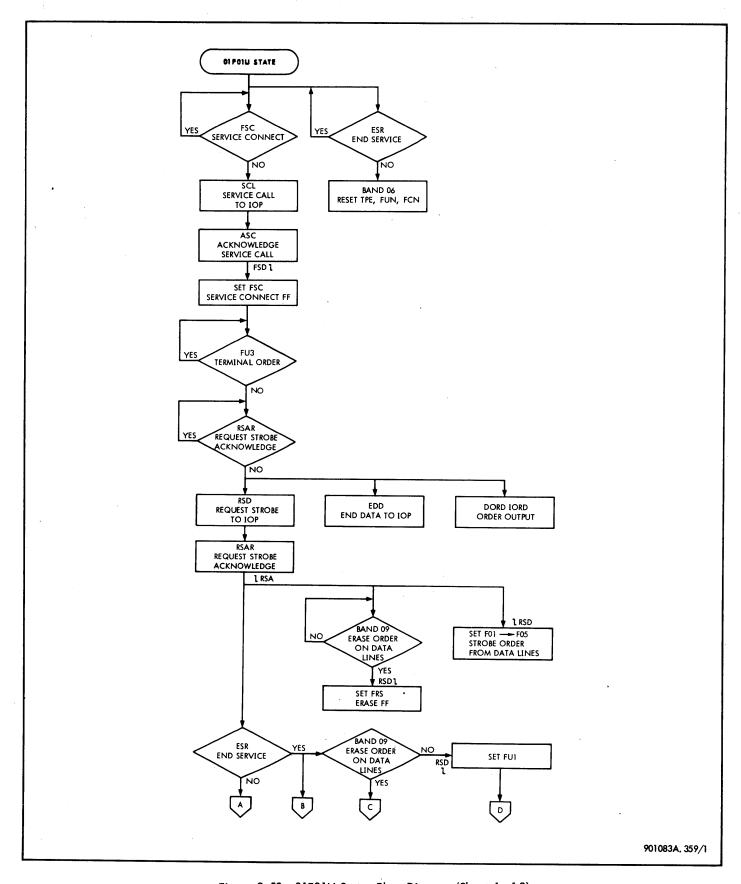

|         | 3-50         | 01F01U, Order Output                                                    | 3-76          |

|         | 3-51         | 01F02U, Waiting for Device Ready                                        | 3-80          |

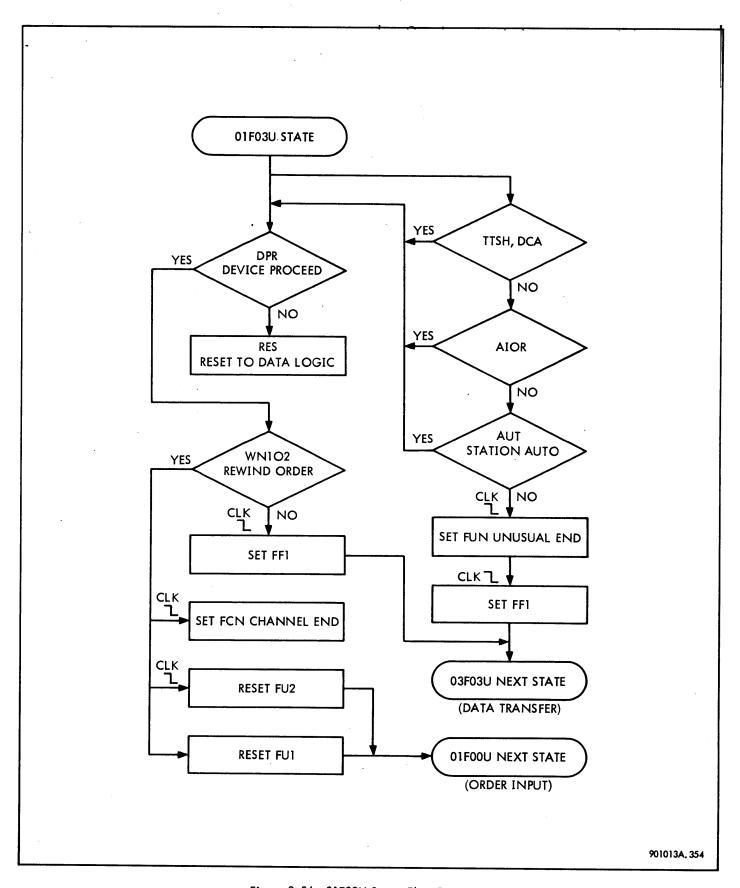

|         | 3-52         | 01F03U, Waiting for Device Proceed                                      | 3-83          |

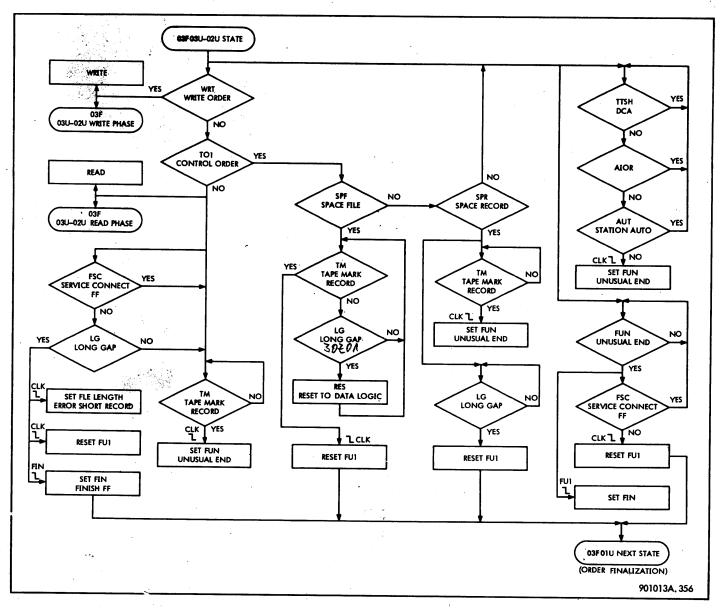

|         | 3-52<br>3-53 | 03F03U-02U, Data Transfer                                               | 3 <b>-</b> 83 |

|         | 3-54         | 03F01U, Order Finalization                                              | 3-63<br>3-88  |

|         | 3-54<br>3-55 | ,                                                                       | 3-88<br>3-90  |

|         | 3-55<br>3-56 | 03F00U, Station Finalization                                            | 3-90<br>3-91  |

|         |              | 01F00U, Order Input                                                     |               |

|         | 3-57         | Magnetic Tape System Functions                                          | 3-95          |

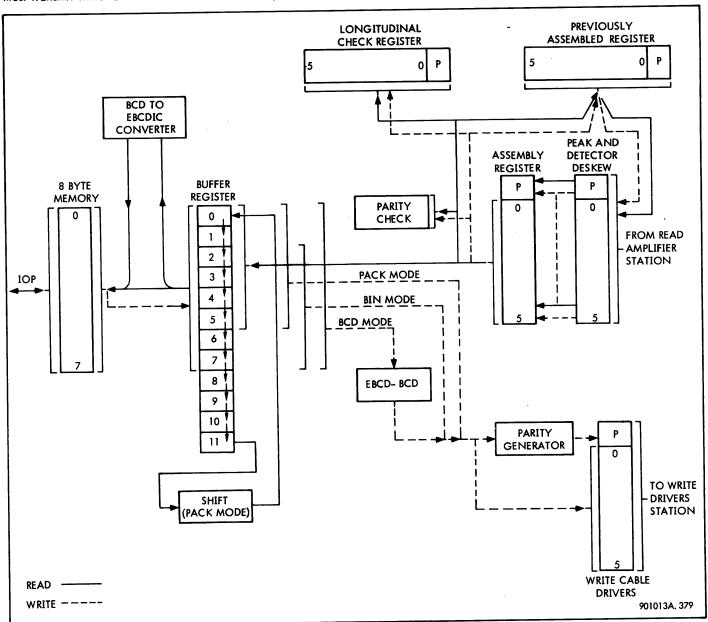

|         | 3-58         | Station Data Electronics                                                | 3-95          |

|         | 3-59         | Writing Operation                                                       | 3-95          |

|         | 3-60         | Reading Operation                                                       | 3-101         |

|         | 3-61         | Controller Data Electronics                                             | 3-105         |

|         | 3-62         | General Description                                                     | 3-105         |

|         | 3-63         | Mode Control                                                            | 3-106         |

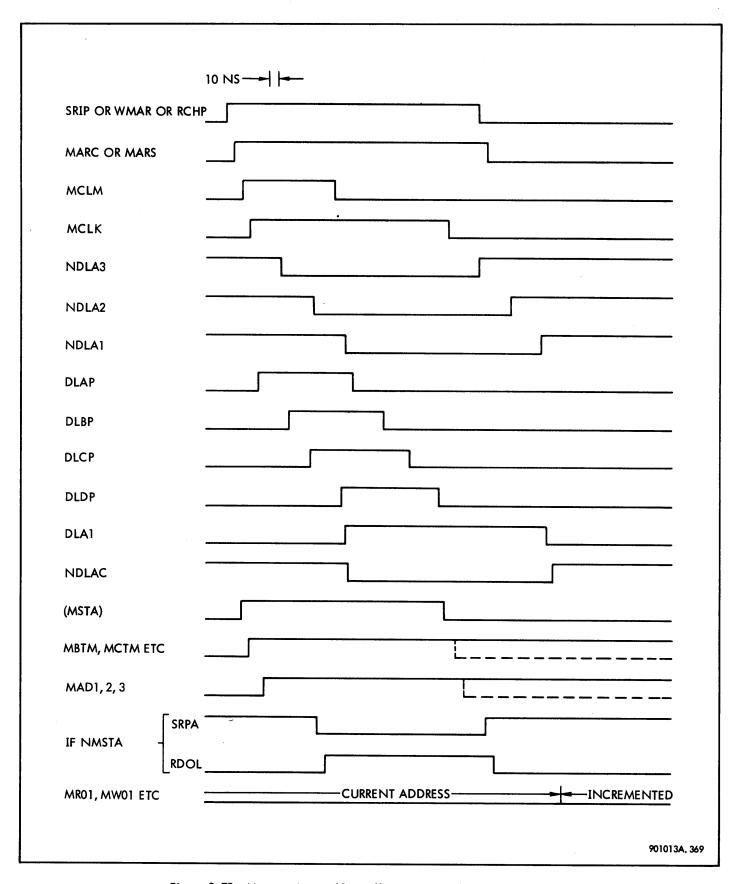

|         | 3-64         | Memory Access                                                           | 3-107         |

|         | 3-65         | Clock Signal                                                            | 3-110         |

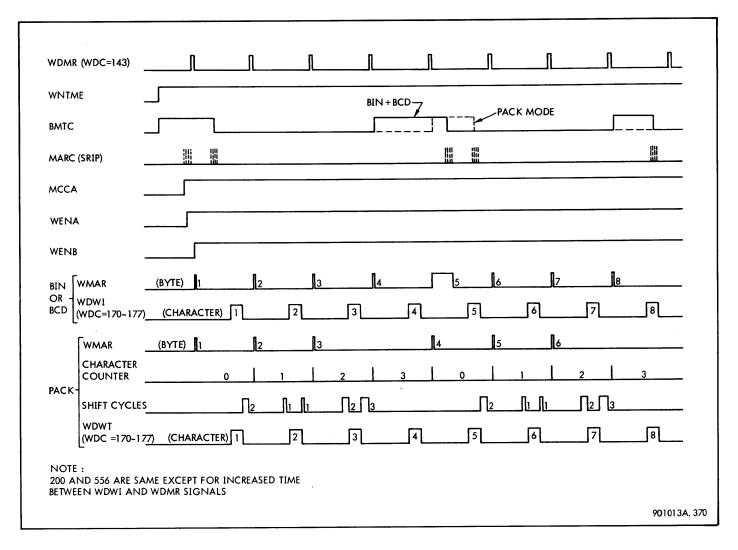

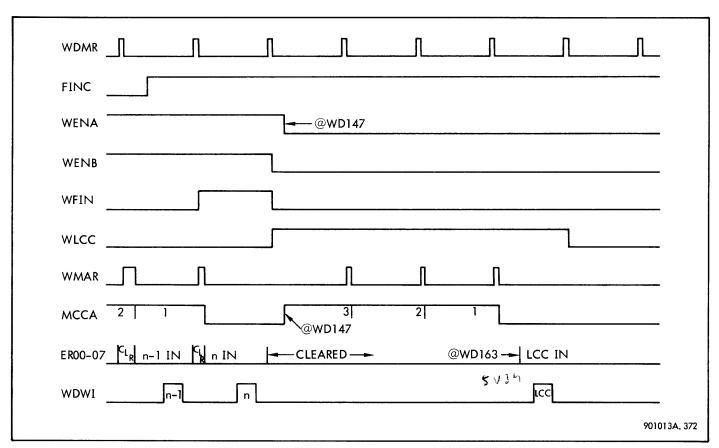

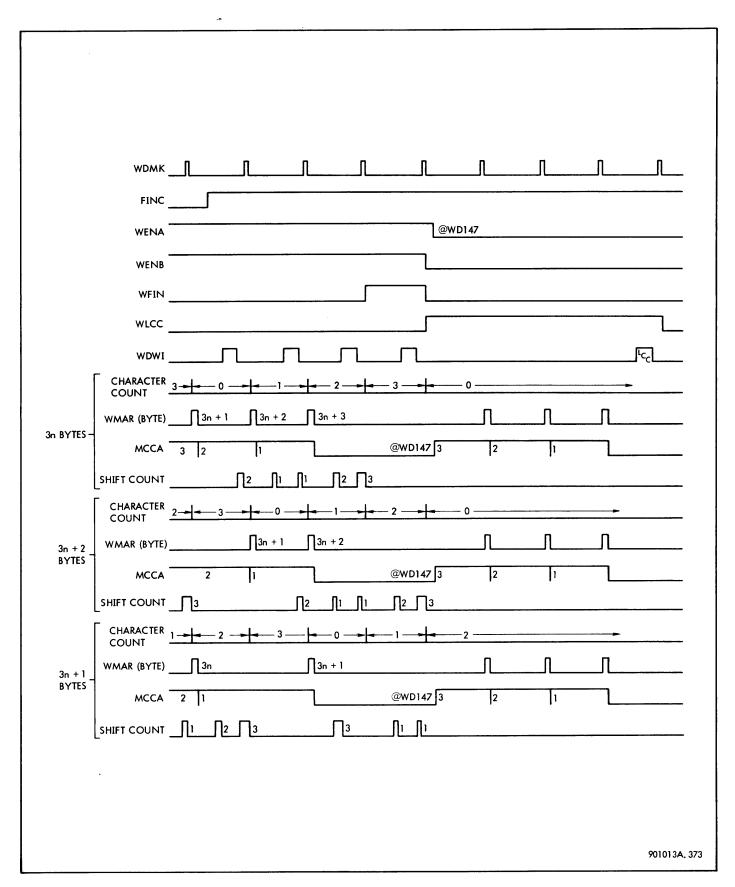

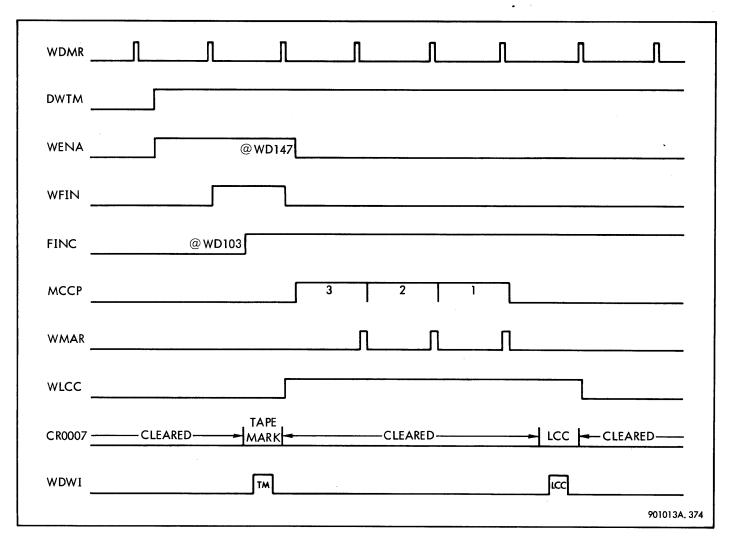

|         | 3-66         | Write Operations                                                        | 3-110         |

|         | 3-67         | Read Operations                                                         | 3-119         |

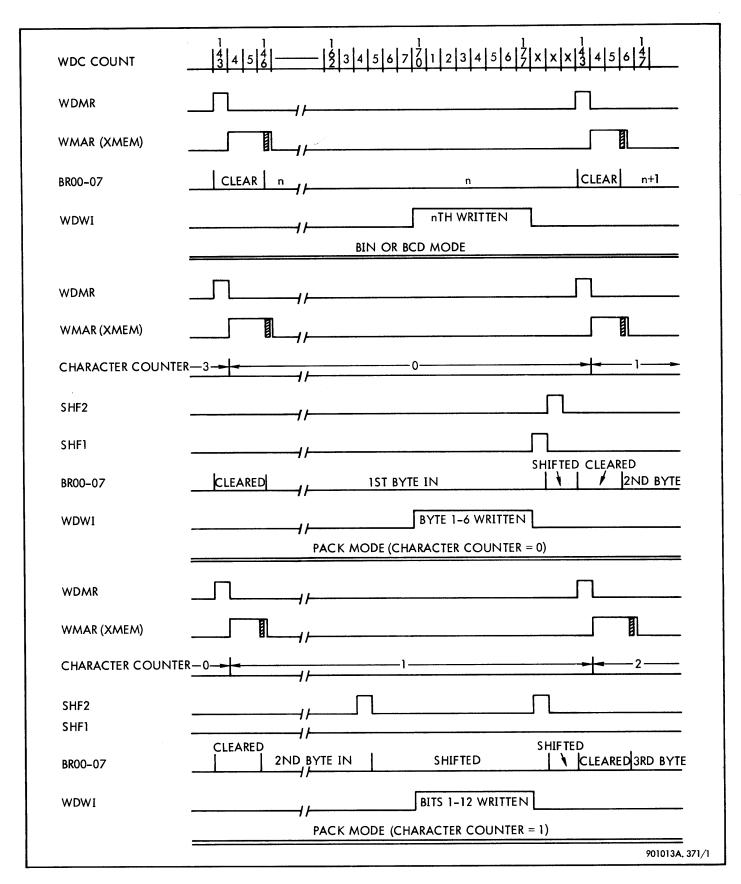

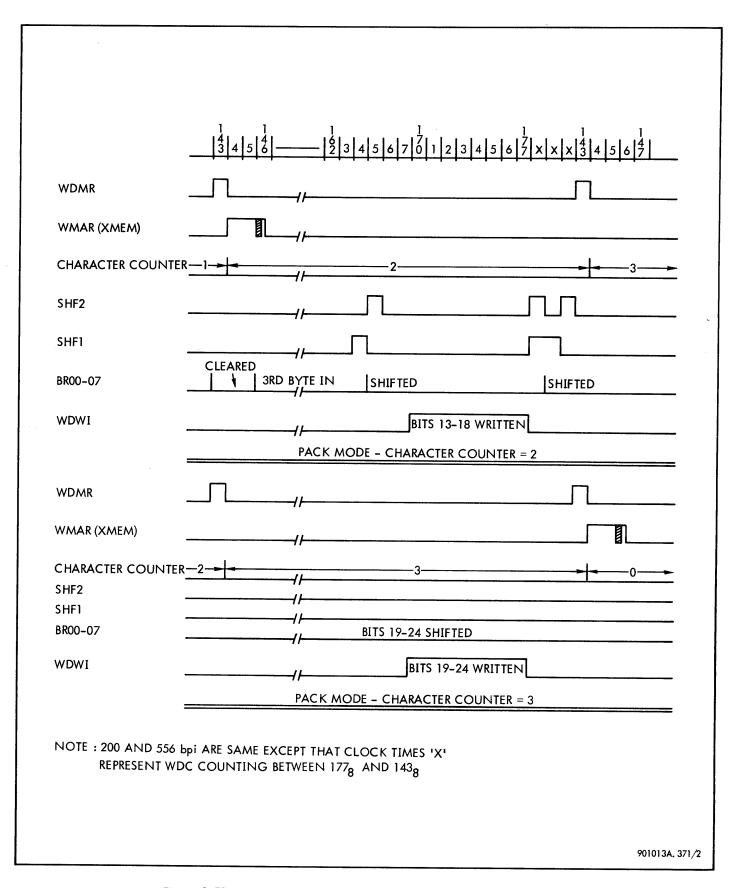

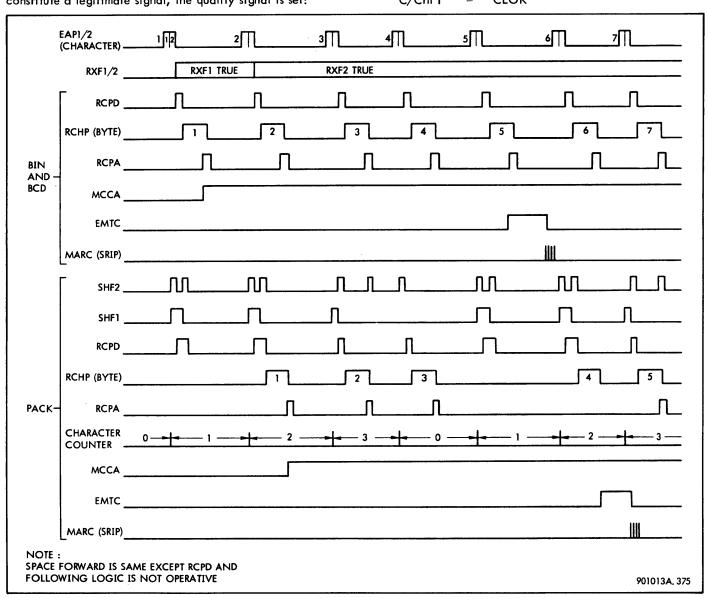

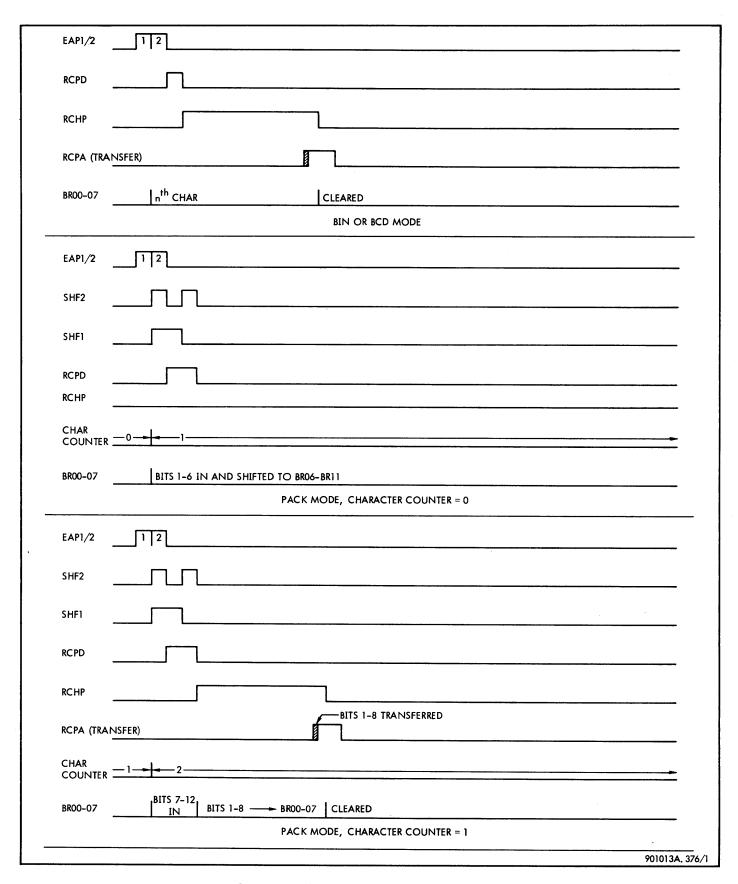

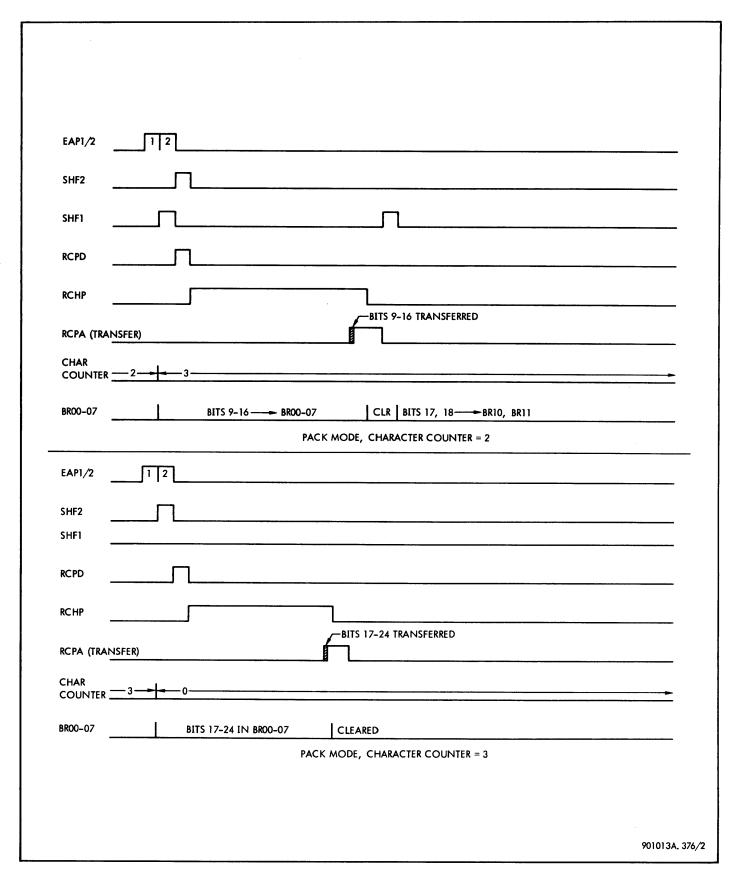

|         | 3-68         | Pack Mode                                                               | 3-130         |

|         | 3-69         | Error Detection                                                         | 3-131         |

|         | 3-70         | BCD-EBCDIC Conversion Charts                                            | 3-133         |

|         | 3-71         | Glossary of Jerms                                                       | 3-136         |

|         | 3-72         | S and Chassis Terms                                                     | 3-136         |

|         | 3-73         | Y and Z Chassis Terms                                                   | 3-138         |

|         | 3-74         | V and W Chassis Terms                                                   | 3-143         |

| IV      | MAINT        | TENANCE AND PARTS LIST                                                  | 4-1           |

|         | 4-1          | Introduction                                                            | 4-1           |

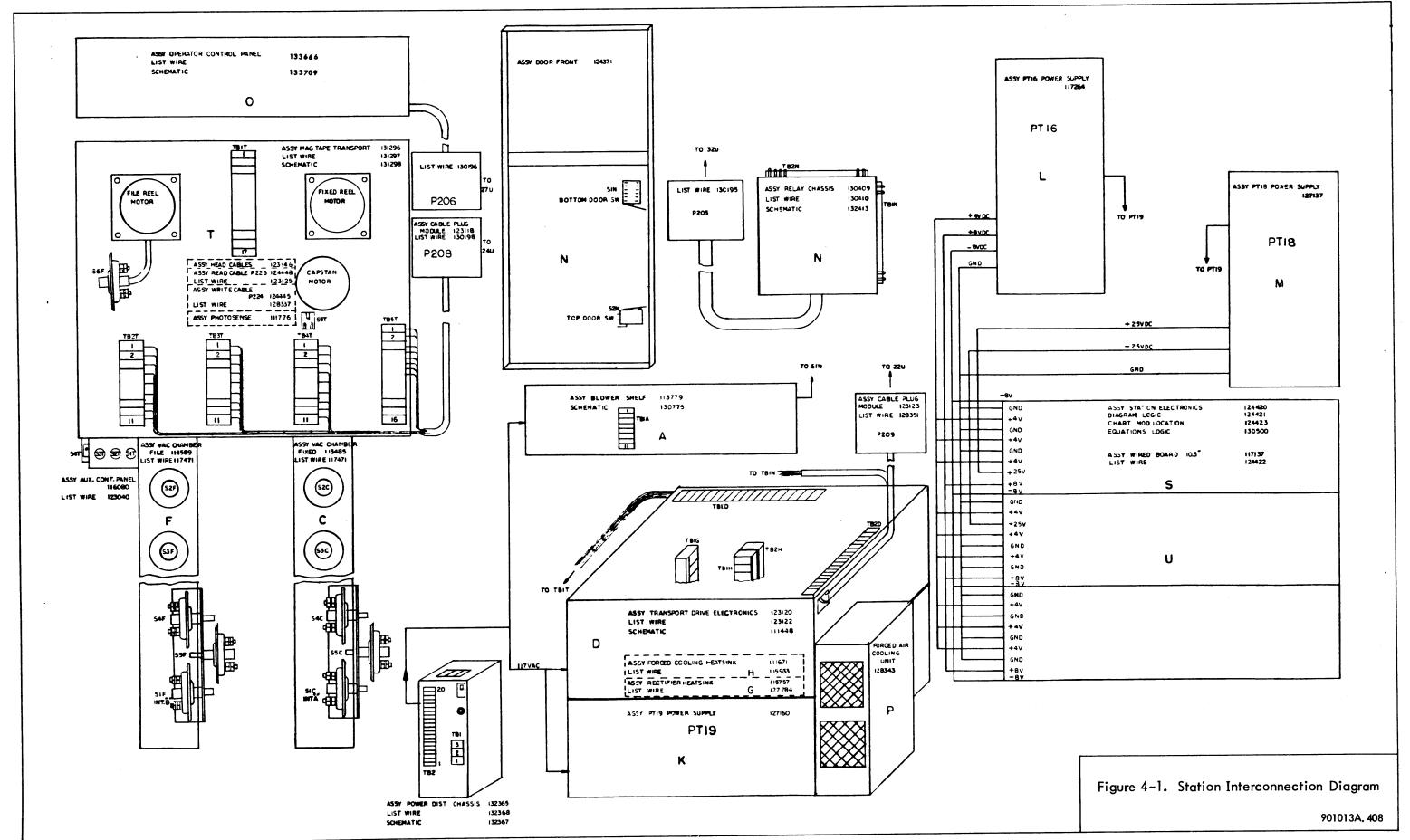

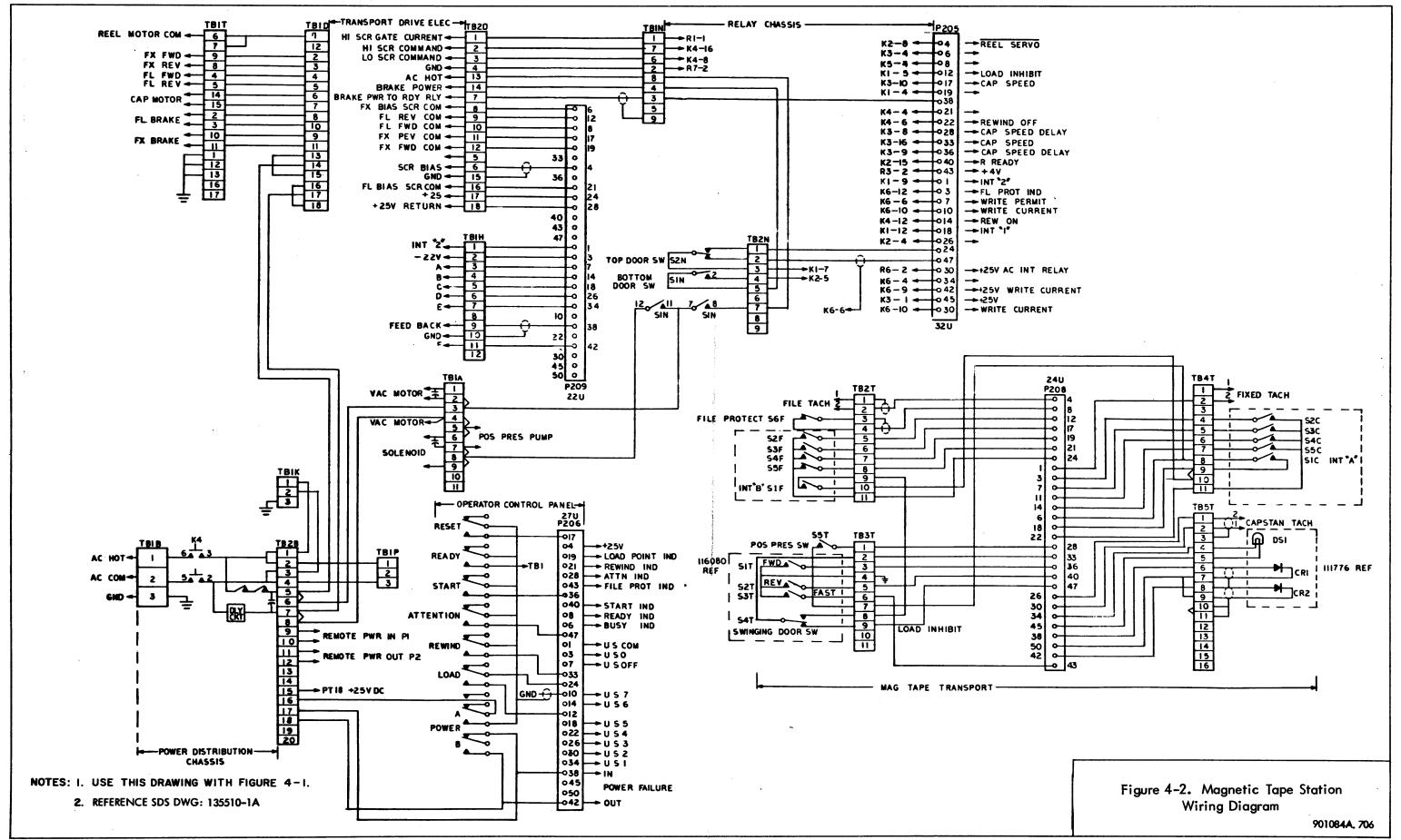

|         | 4-2          | Cabling                                                                 | 4-1           |

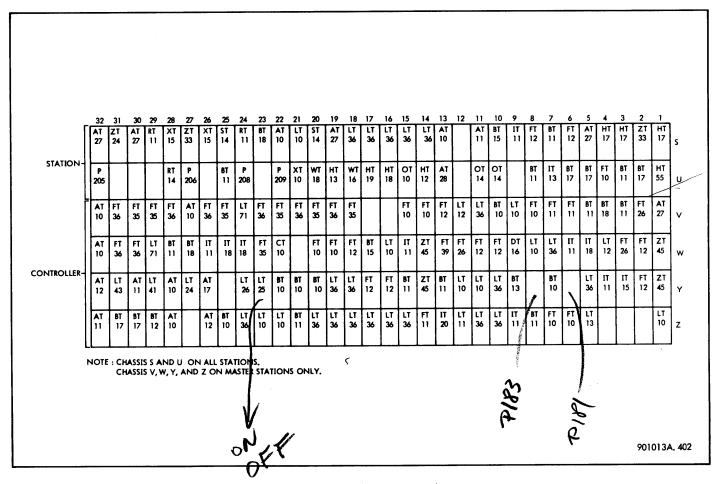

|         | 4-3          | Module Location                                                         | 4-1           |

|         | 4-4          | Preventive Maintenance                                                  | 4-6           |

|         | 4-5          | Cleaning Procedures                                                     | 4-6           |

|         | 4-6          | Corrective Maintenance                                                  | 4-9           |

|         | 4-7          | Preliminary Checks                                                      | 4-9           |

|         | 4-8          | Resistance Checks                                                       | 4-9-          |

|         | 4-9          | Voltage Check                                                           | 4-9           |

|         | 4-10         | Mechanical Adjustments                                                  | 4-10          |

|         | 4-11         | Vacuum Chamber Door Adjustment                                          | 4-10          |

|         | 4-12         | Vacuum Level Adjustment                                                 | 4-10          |

|         | 4-13         | Vacuum Valve Adjustment                                                 | 4-10          |

|         | 4-14         | Write Enable (File Protect) Switch Adjustment                           | 4-10          |

|         | 4-15         | Positive Pressure Adjustment                                            | 4-10          |

|         | 4-16         | Head Cover Actuator Adjustment                                          | 4-10          |

|         | 4-17         | File Reel Hub Holddown Adjustment · · · · · · · · · · · · · · · · · · · | 4-11          |

|         | 4-18         | Fixed Reel Check                                                        | 4-11          |

|         | 4-19         | Reel Motor Drag Torque                                                  | 4-11          |

|         |              |                                                                         | 7-11          |

### SDS 901013

### Contents

| Section |                       | Title                                                                      | Page         |

|---------|-----------------------|----------------------------------------------------------------------------|--------------|

|         | 4-20                  | Electrical Adjustments, Transport                                          | 4-11         |

|         | 4-20<br>4-21          | Transport Clock Adjustment                                                 | 4-11         |

|         | 4-21<br>4 <b>-</b> 22 | Photosense Lamp Current, BOT and EOT Adjustments                           | 4-11         |

|         | 4-22<br>4-23          | Capstan Dead Band Adjustment                                               | 4-12         |

|         |                       | Preliminary Capstan Speed Adjustment                                       | 4-12         |

|         | 4-24<br>4-25          | Oscillation Check                                                          | 4-12         |

|         |                       | Reel Servo Amplifiers Zero Adjustment                                      | 4-12         |

|         | 4-26<br>4-27          | Fixed Reel Servo Amplifier Tape Loop Positioning Adjustment                | 4-12         |

|         | 4-27<br>4-28          | File Reel Servo Amplifier Tape Loop Positioning Adjustment                 | 4-13         |

|         | 4-26<br>4-29          | Load One-Shot Adjustment (SAS and 0, 22 Sec One-Shots)                     | 4-13         |

|         | 4-27                  | Load Function Test                                                         | 4-13         |

|         | 4-30<br>4-31          | Rewind One-Shot Adjustment (0.8 Sec O-S, Both Delay, Backups, and F Delay) | 4-14         |

|         | 4-31<br>4-32          | Write Enable (File Protect) Check                                          | 4-14         |

|         | 4-32                  | Electrical Adjustments, Controller                                         | 4-14         |

|         | 4-34                  | Module Location                                                            | 4-14         |

|         | 4-35                  | Clock Oscillator Check                                                     | 4-14         |

|         | 4-36                  | Controller Checkout With IOP                                               | 4-15         |

|         | 4-37                  | Station Logic Adjustments                                                  | 4-15         |

|         | 4-38                  | Tape Tracking                                                              | 4-15         |

|         | 4-39                  | Capstan Speed Check and Adjustment                                         | 4-15         |

|         | 4-40                  | Ramp Adjustment for Acceleration and Deceleration                          | 4-16         |

|         | 4-41                  | Master Clock                                                               | 4-18         |

|         | 4-42                  | Delay Counter                                                              | 4-18         |

|         | 4-43                  | Device Ready Latch                                                         | 4-18         |

|         | 4-44                  | Station Address Selection                                                  | 4-19         |

|         | 4-45                  | Station Connect                                                            | 4-19         |

|         | 4-46                  | Starting Delay Check                                                       | 4-20         |

|         | 4-47                  | Read/Write Amplifiers                                                      | 4-20         |

|         | 4-48                  | Threshold Adjustment For Read Amplifiers                                   | 4-21         |

|         | 4-49                  | Deskew Adjustment                                                          | 4-22         |

|         | 4-50                  | Forward Read Deskew                                                        | 4-22         |

|         | 4-51                  | Reverse Read Deskew                                                        | 4-23         |

|         | 4-52                  | Write Deskew                                                               | 4-23         |

|         | 4-53                  | Ending Delay Check                                                         | 4-23         |

|         | 4-54                  | Operator Control Panel Indicator Check                                     | 4-24         |

|         | 4-55                  | Peripheral Equipment Tester Operation                                      | 4-24         |

|         | 4-56                  | Preparation and Connection                                                 | 4-24<br>4-25 |

|         | 4-57                  | Overlay                                                                    | 4-25         |

|         | 4-58                  | On-Line/Off-Line Switch                                                    | 4-25         |

|         | 4-59                  | Write Operation                                                            | 4-25         |

|         | 4-60                  | Read Forward Operation                                                     | 4-25         |

|         | 4-61                  | Space Reverse Operation                                                    | 4-25         |

|         | 4-62                  | Removal and Replacement Procedures                                         | 4-25         |

|         | 4-63                  | Tape Guide Removal and Replacement                                         | 4-31         |

|         | 4-64                  | Reel Motor Brake Removal and Replacement                                   | 4-32         |

|         | 4-65                  | Reel Motor Brake Adjustment                                                | 4-32         |

|         | 4-66                  | File Reel Holddown Knob Removal and Replacement                            | 4-35         |

|         | 4-67                  | Fixed Reel Removal and Replacement                                         | 4-36         |

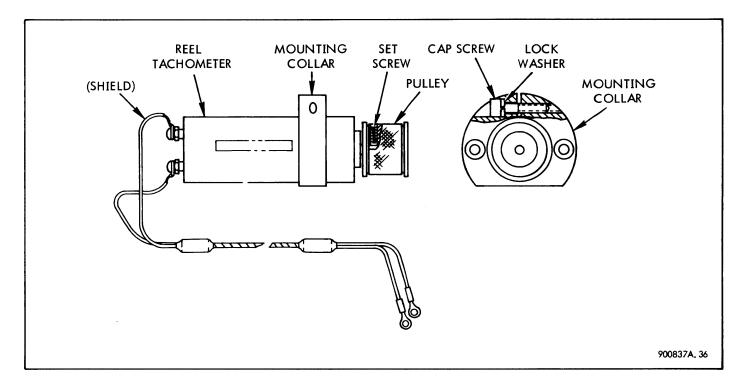

|         | 4-68                  | Reel Tachometer Removal and Replacement                                    | 4-36         |

|         | 4-69                  | Capstan Motor Removal and Replacement                                      | 4-37         |

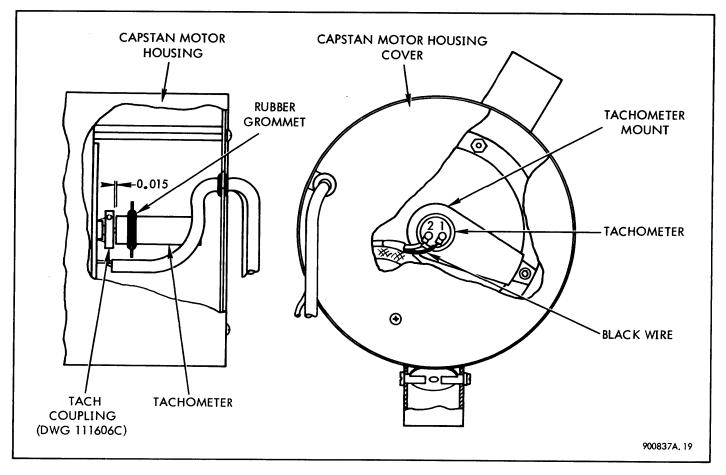

|         | 4-70<br>4-71          | Capstan Tachometer Removal and Replacement                                 | 4-37         |

|         | 4-71<br>4-72          | Positive Pressure Pump Removal and Replacement                             | 4-38         |

|         | 4-72<br>4-73          | Reel Motor Removal and Replacement                                         | 4-38         |

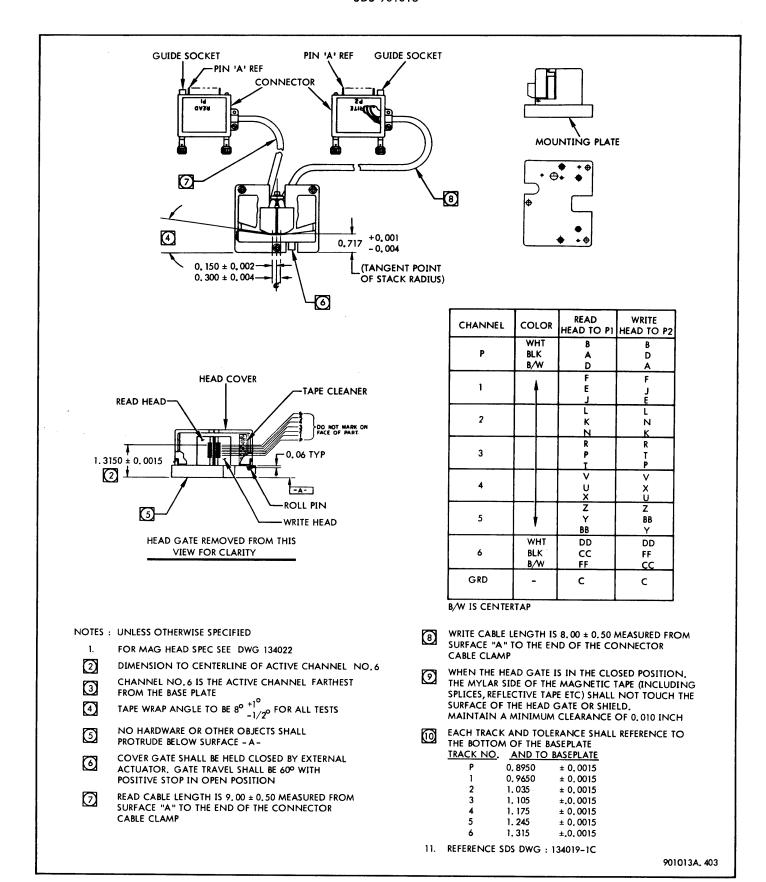

|         | 4-73<br>4-74          | Read/Write Head Removal and Replacement                                    | 4-39         |

|         | T-/T                  | treated trains treated terms of the fi                                     |              |

### SDS 901013

| Section               | Title                                                           | Page         |

|-----------------------|-----------------------------------------------------------------|--------------|

|                       | 4-75 Photosense Removal and Replacement                         | 4-39         |

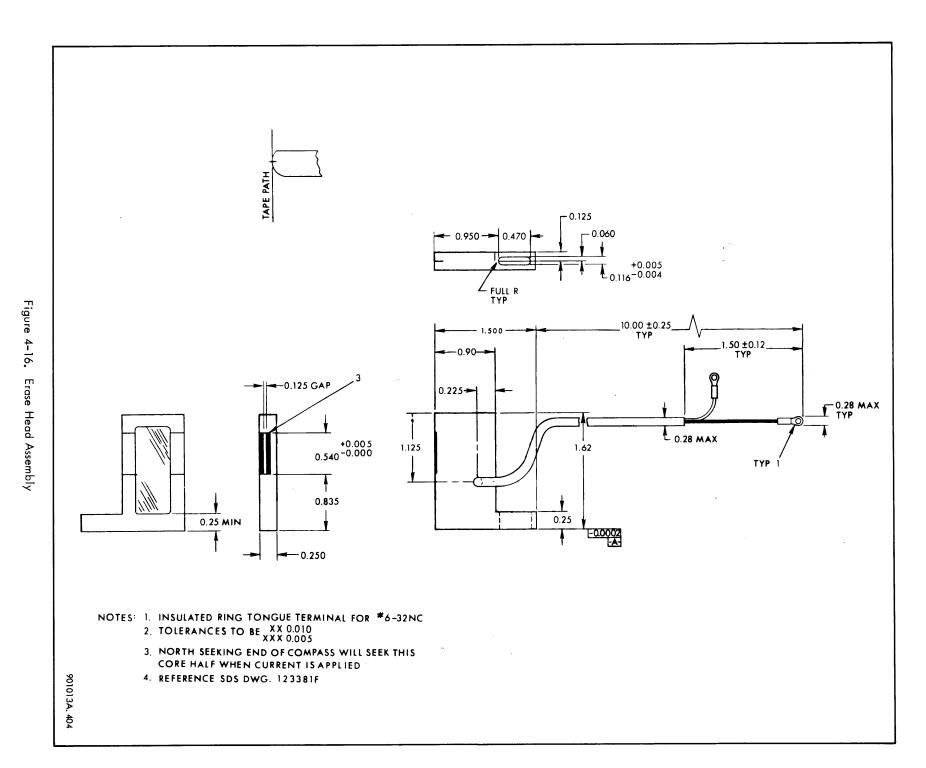

|                       | 4-76 Erase Head Removal and Replacement                         | 4-39         |

|                       | 4-77 Parts List                                                 | 4-39         |

|                       | 4–78 Tabular Listings                                           | 4-39         |

|                       | 4-79 Illustrations                                              | 4-40         |

|                       | 4–80 Manufacturer Code Index                                    | 4-40         |

|                       | LIST OF ILLUSTRATIONS                                           |              |

| Figure                | Title                                                           | Page         |

| 1-1                   | Magnetic Tape System Model 7371/7372/7374, Front and Side Views | 1-2          |

| 1-2                   | Magnetic Tape System Model 7371/7372/7374, Rear View            | 1-3          |

| 1-3                   | Magnetic Tape System Block Diagram                              | 1 –5         |

| 1-4                   | Physical Spacing on Tape                                        | 1 –5         |

| 2-1                   | Operator Control Panel, Front View                              | 2-1          |

| 2-2                   | Interlock Network                                               | 2-5          |

| 2-3                   | Location of Reflective Tape Markers                             | 2-6          |

| 2-4                   | File Reel and File Protect Ring                                 | 2-6          |

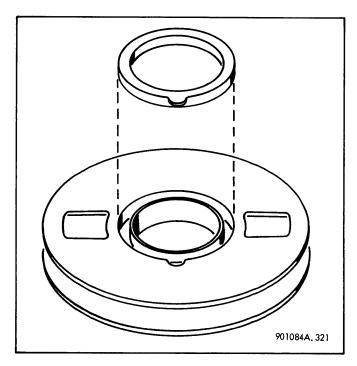

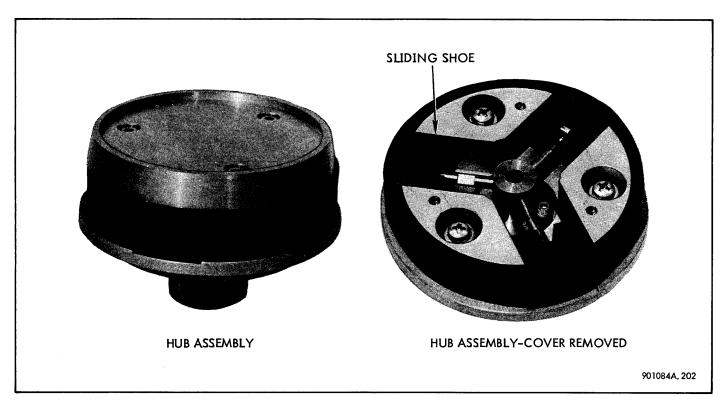

| 2-5                   | POPO Hub Assembly                                               | 2-7          |

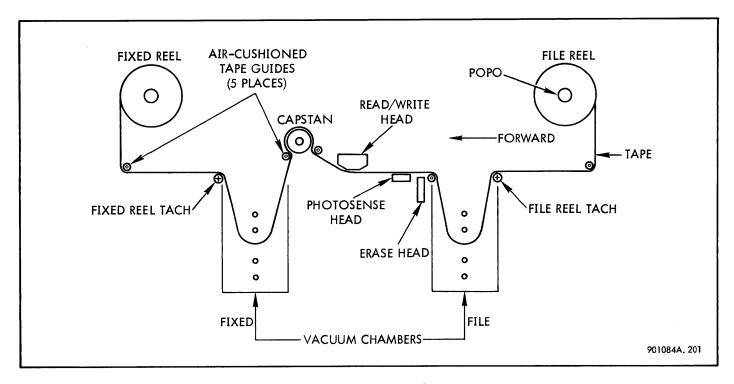

| 2-6                   | Tape Path                                                       | 2-8          |

| 2-7                   | Control Line, Flow Chart                                        | 2-14         |

| 3-1                   | Data Representation on Tape, Binary Mode                        | 3-2          |

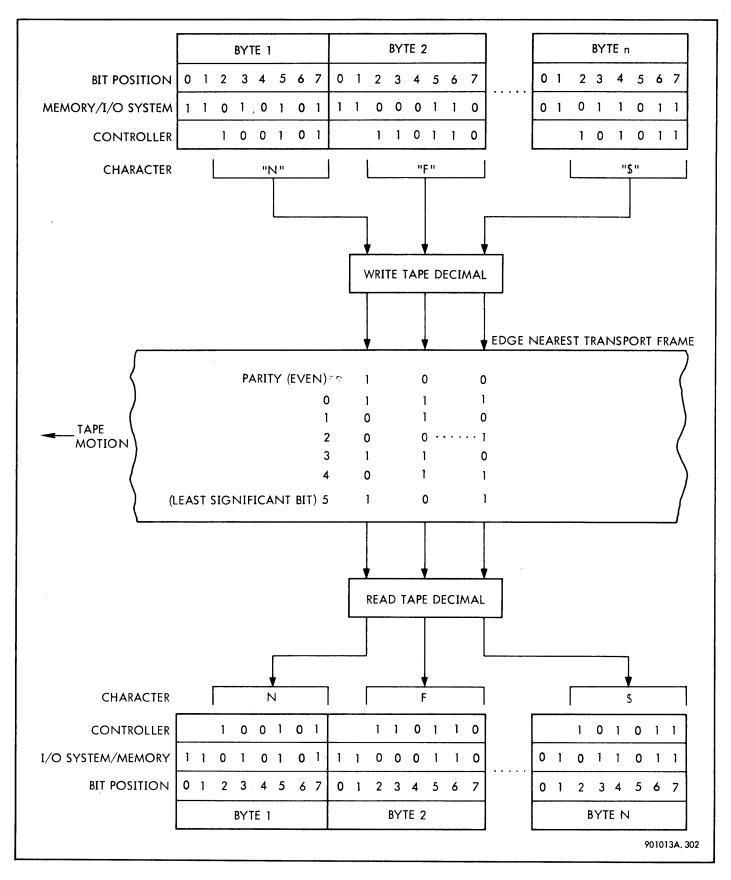

| 3-2                   | Data Representation on Tape, Decimal Mode                       | 3-3<br>3-5   |

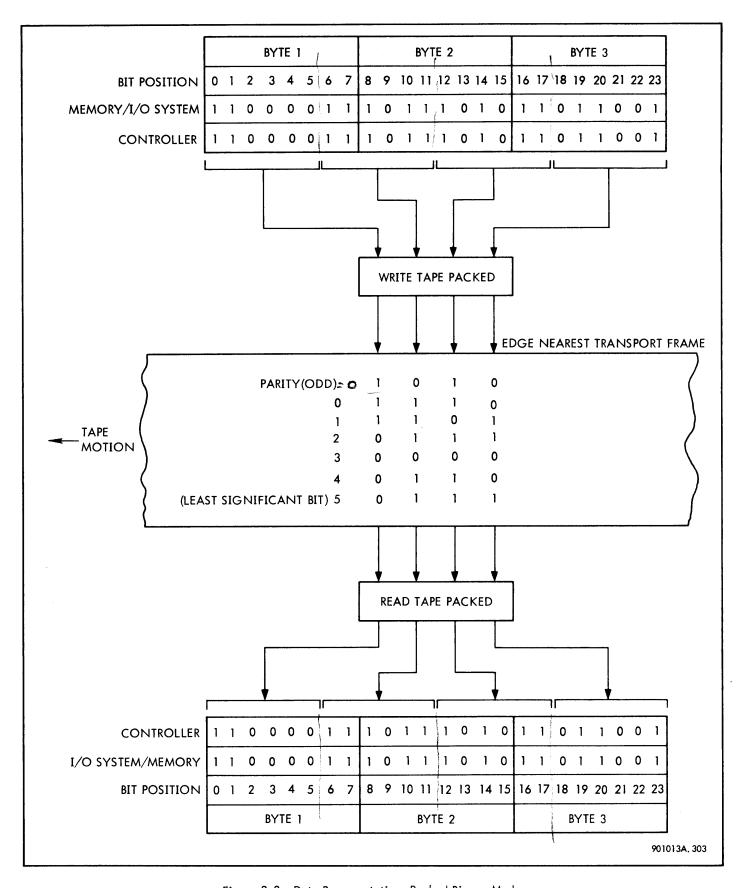

| 3-3                   | Data Representation, Packed Binary Mode                         | 3-3<br>3-7   |

| 3-4<br>3-5            | Power Distribution Chassis, Schematic Diagram                   | 3-10         |

| 3-5<br>3-6            | Magnetic Tape Transport, Back View                              | 3-10         |

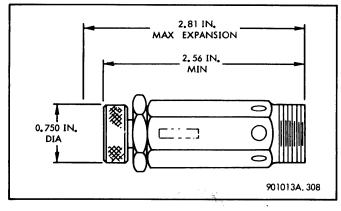

| 3 <b>-</b> 6          | Pressure Regulator                                              | 3-12         |

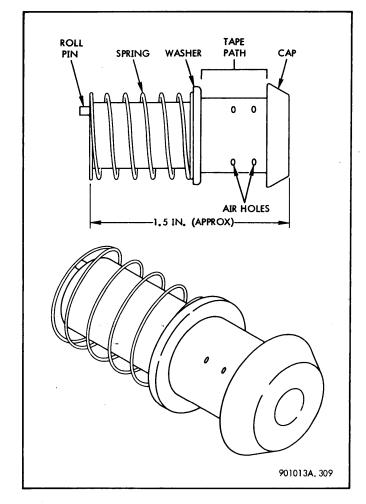

| 3-8                   | Tape Guide                                                      | 3-12         |

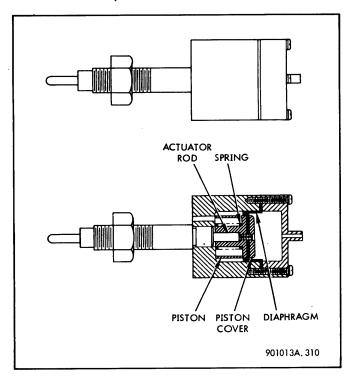

| 3-9                   | Head Cover Actuator                                             | 3-13         |

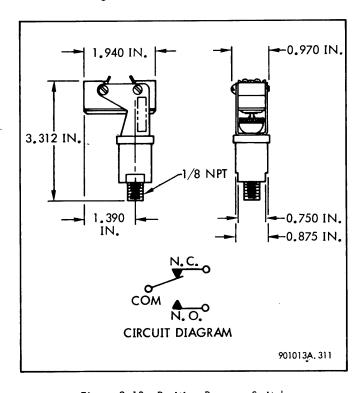

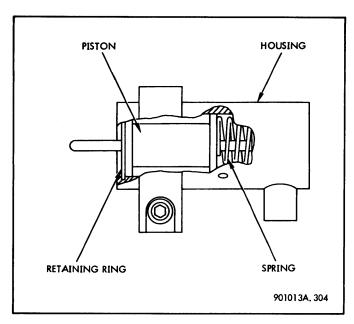

| 3-10                  | Positive Pressure Switch                                        | 3-13         |

| 3-11                  | Write Enable Switch Actuator                                    | 3-14         |

| 3-12                  | Relay and Interlock Functional Diagram                          | 3-15         |

| 3-13                  | Station Transport Motion Control, Block Diagram                 | 3-17         |

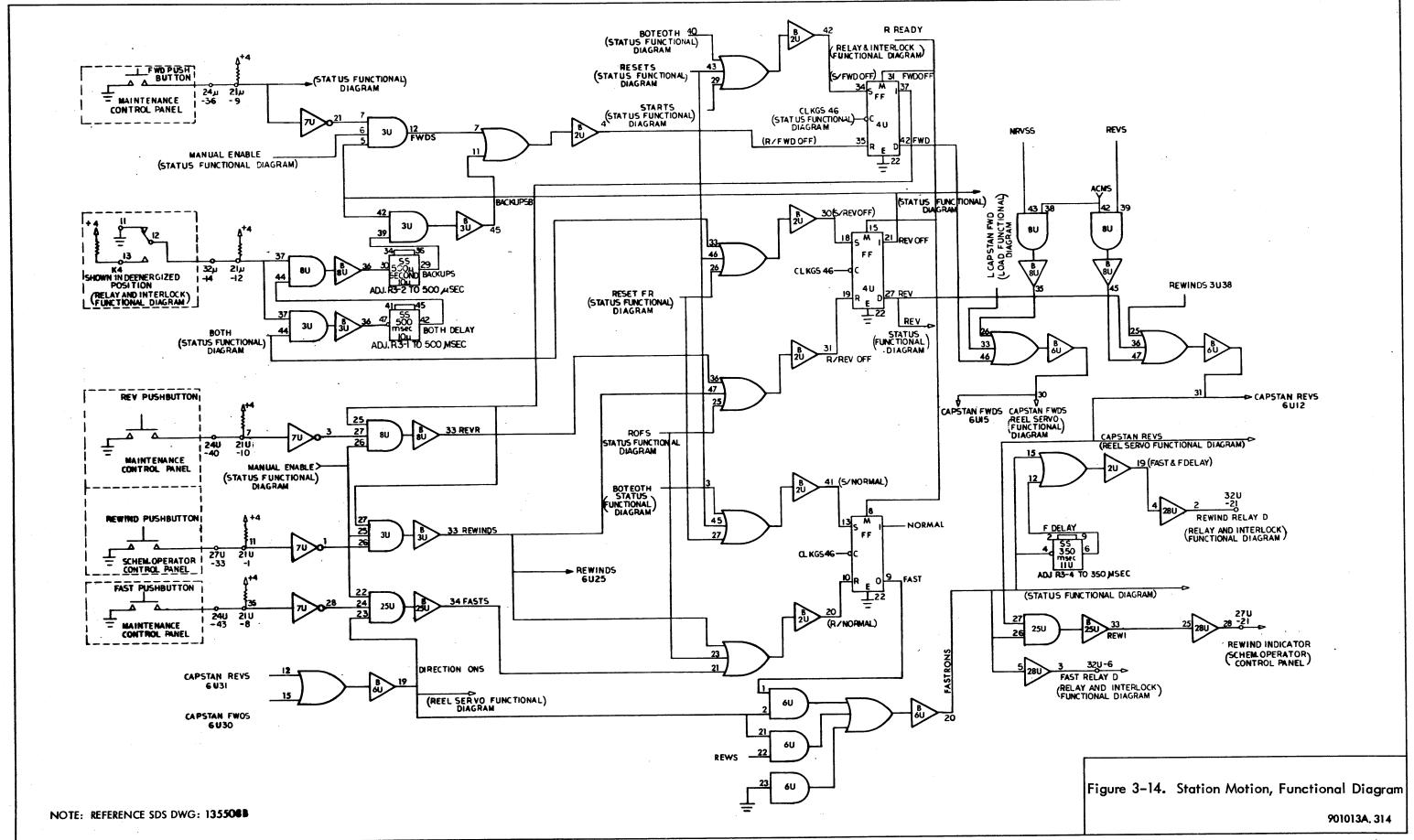

| 3-14                  | Station Motion, Functional Diagram                              | 3-19         |

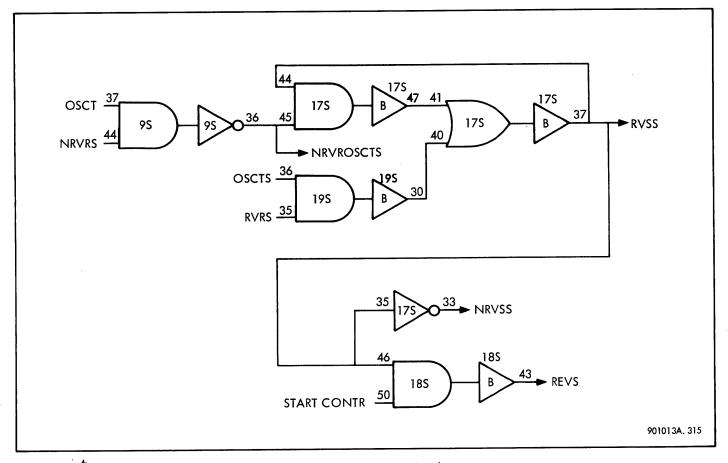

| 3-15                  | Direction Latch                                                 | 3-21         |

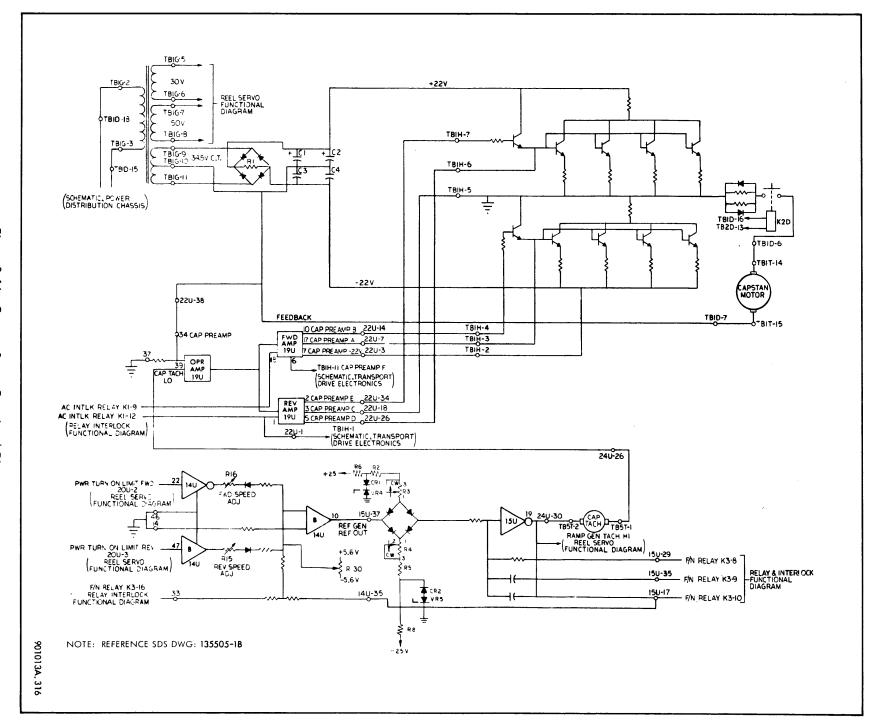

| 3-16                  | Capstan Servo, Functional Diagram                               | 3-22         |

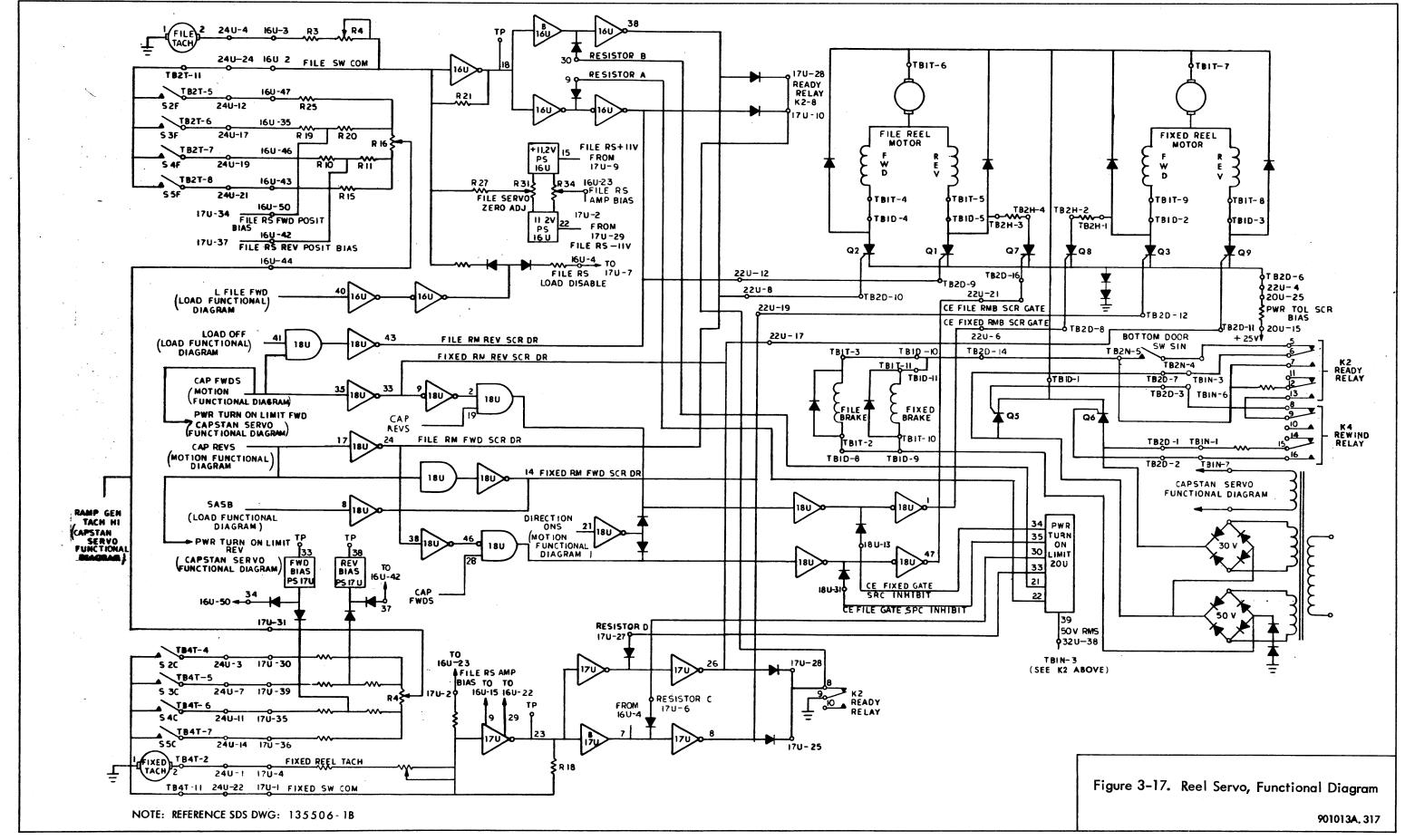

| 3-17                  | Reel Servo, Functional Diagram                                  | 3-25         |

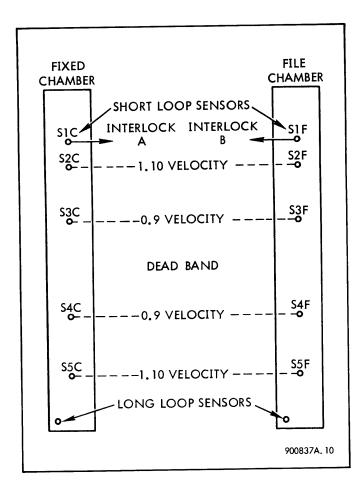

| 3-18                  | Vacuum Chamber, Tape Position Switches                          | 3-27         |

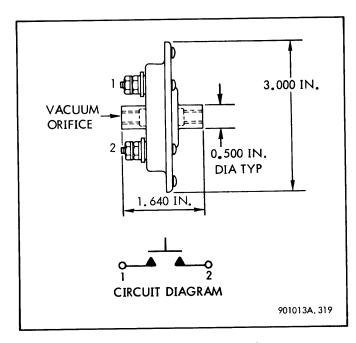

| 3-19                  | Vacuum Switch                                                   | 3-27<br>3-30 |

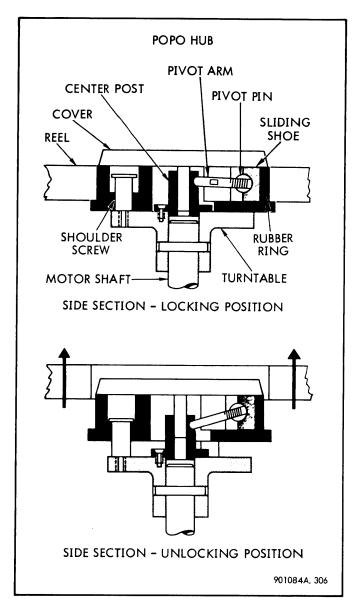

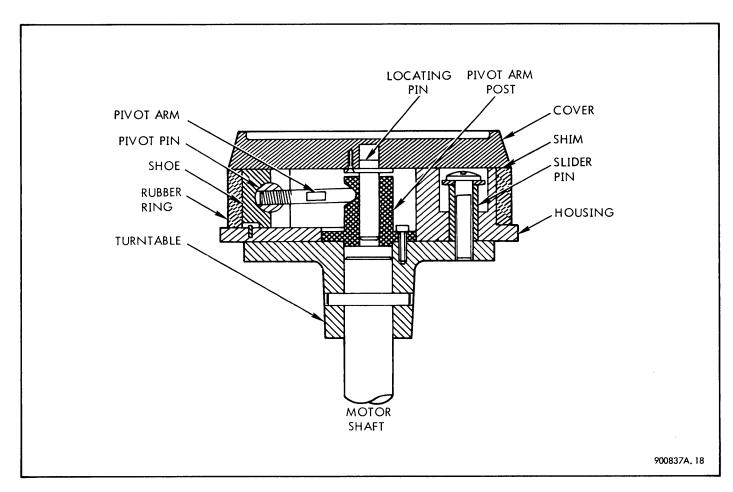

| 3-20                  | POPO Hub Assembly                                               | 3-30         |

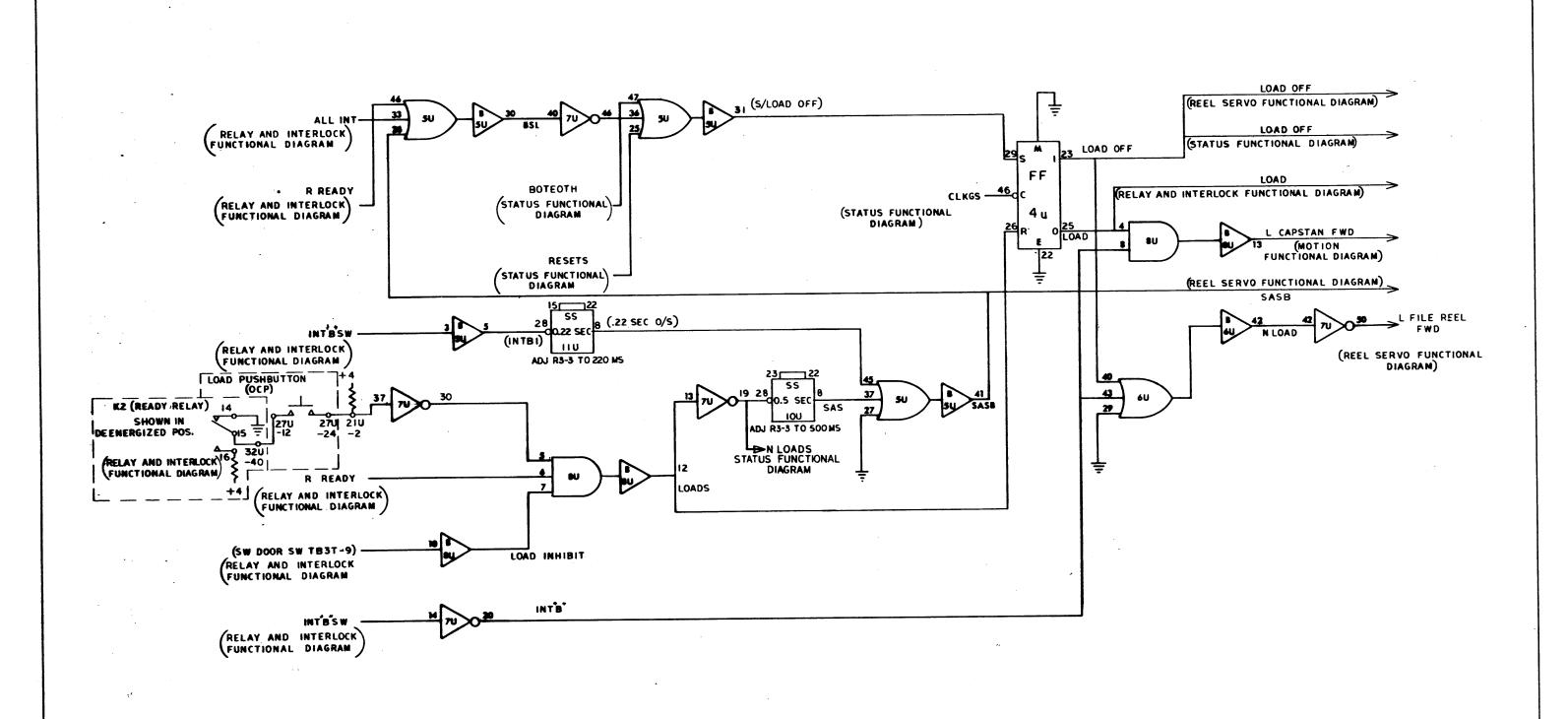

| 3-21                  | Load, Functional Diagram                                        | 3-35         |

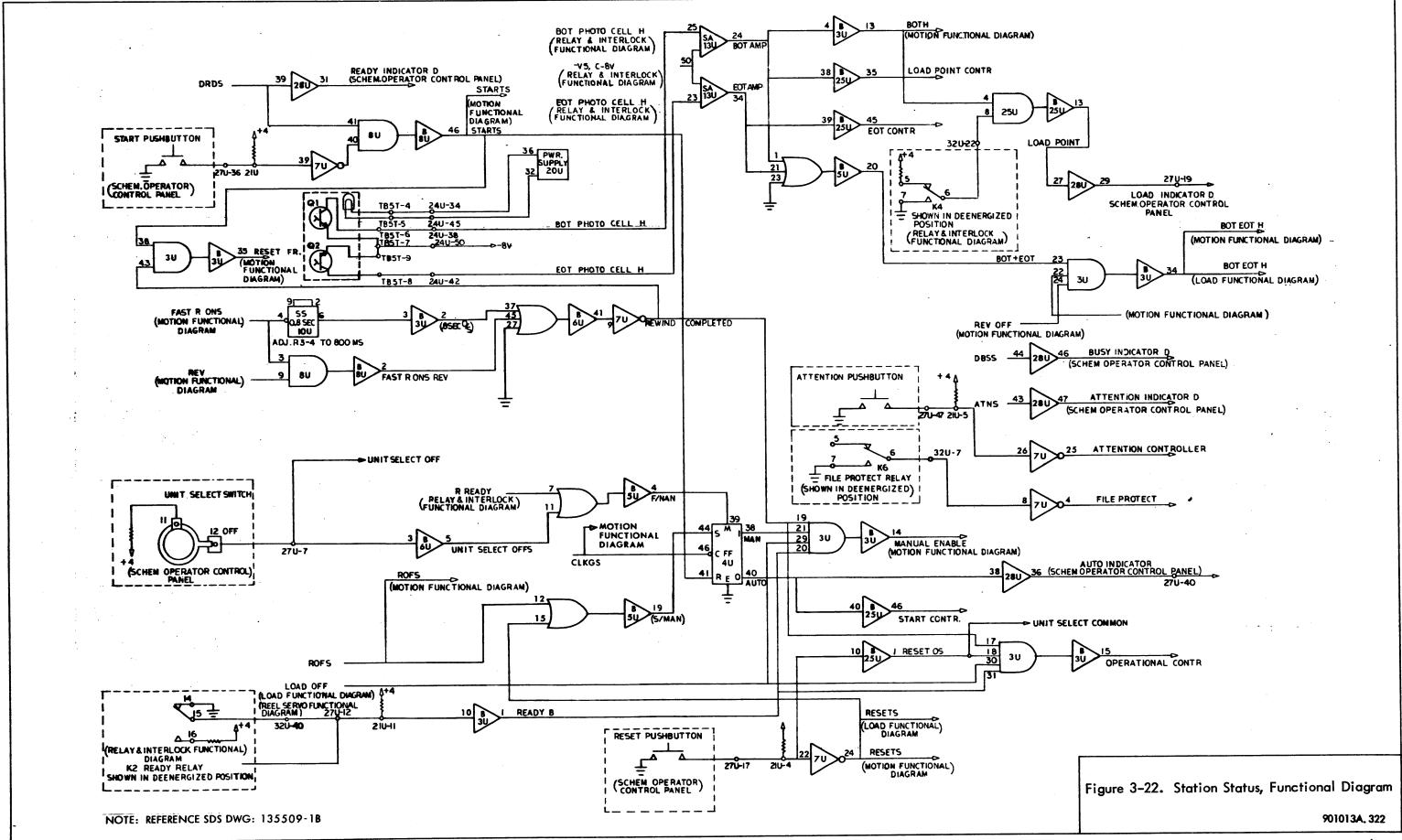

| 3-22<br>3-23          | Station Status, Functional Diagram                              | 3-37         |

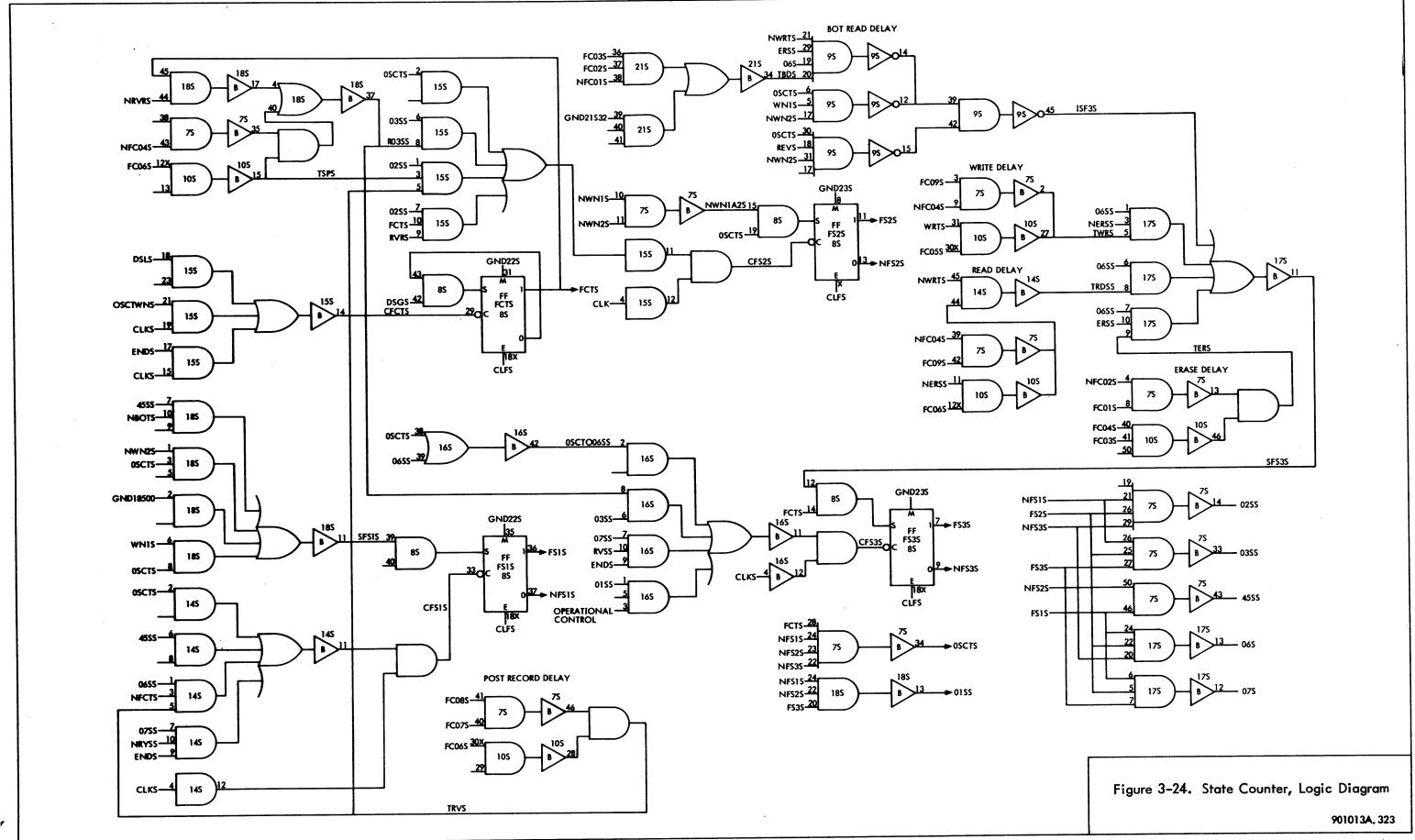

| 3-23<br>3 <b>-</b> 24 | State Counter, Logic Diagram                                    | 3-39         |

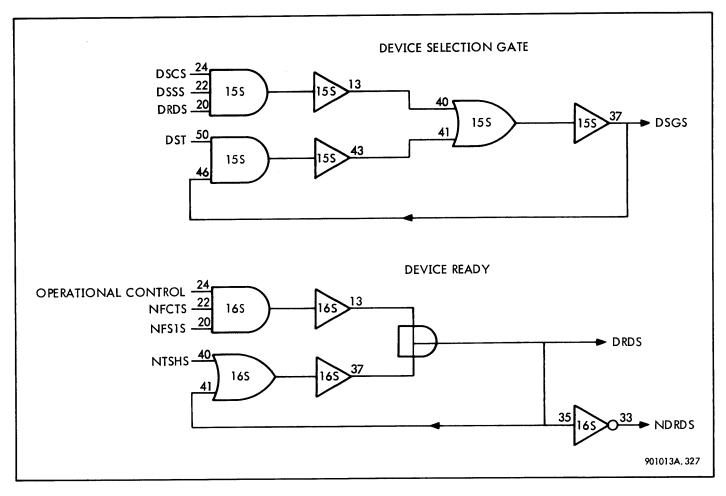

| 3-25                  | Device Selection and Device Ready, Logic Diagram                | 3-42         |

| 3 <b>-</b> 25         | Rewind On-Line With Interrupt, Block Diagram                    | 3-44         |

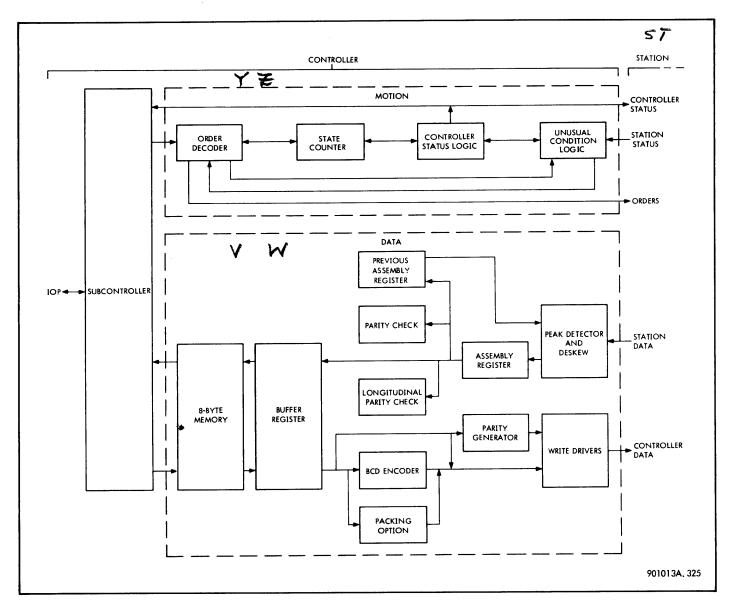

| 3-27                  | Magnetic Tape Controller, Block Diagram                         | 3-46         |

| 3-28                  | Magnetic Tape Controller States, Simplified Block Diagram       | 3-47         |

| 3-29                  | Subcontroller, Simplified Functional Block Diagram              | 3-48         |

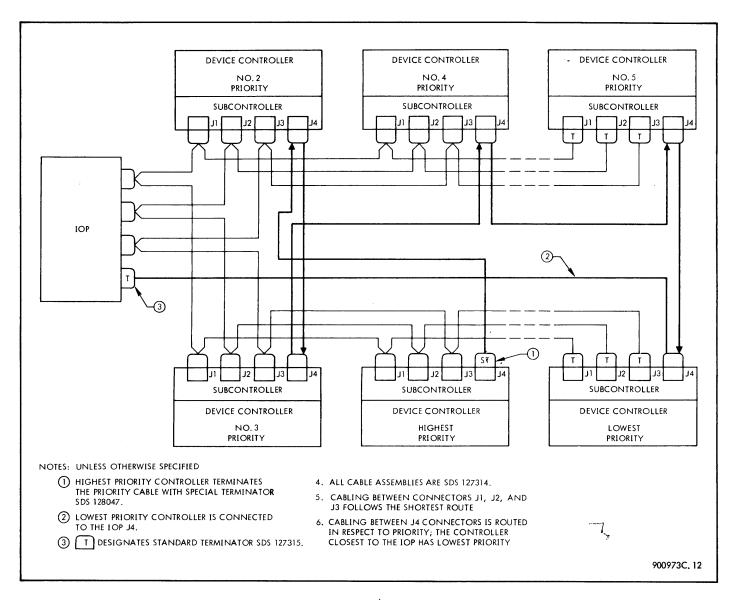

| 3-30                  | Typical I/O Interconnection                                     | 3-49         |

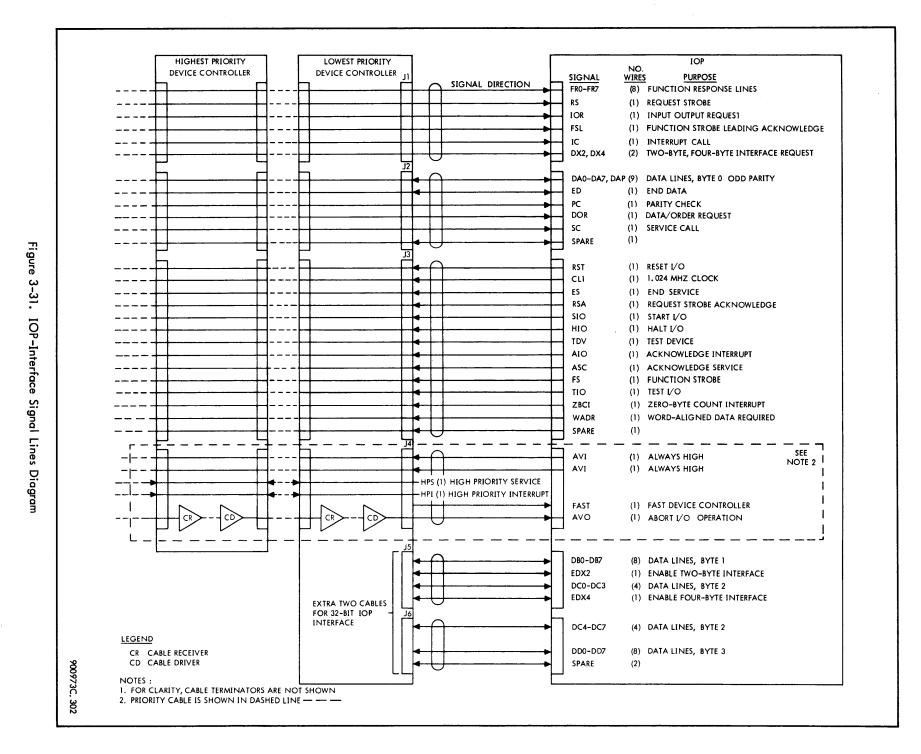

| 3-31                  | IOP-Interface Signal Lines Diagram                              | 3-50         |

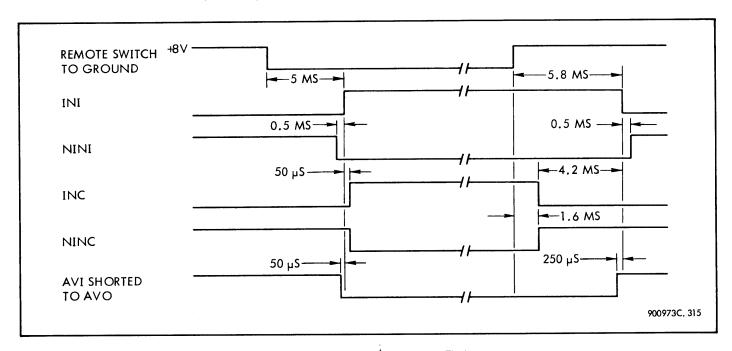

| 3-32                  | Connect/Disconnect Timing                                       | 3-56         |

| 3-33                  | Communication and Service Cycle Sequence                        | 3-57         |

### LIST OF ILLUSTRATIONS (Cont.)

| igure         | Title                                                            | Page          |

|---------------|------------------------------------------------------------------|---------------|

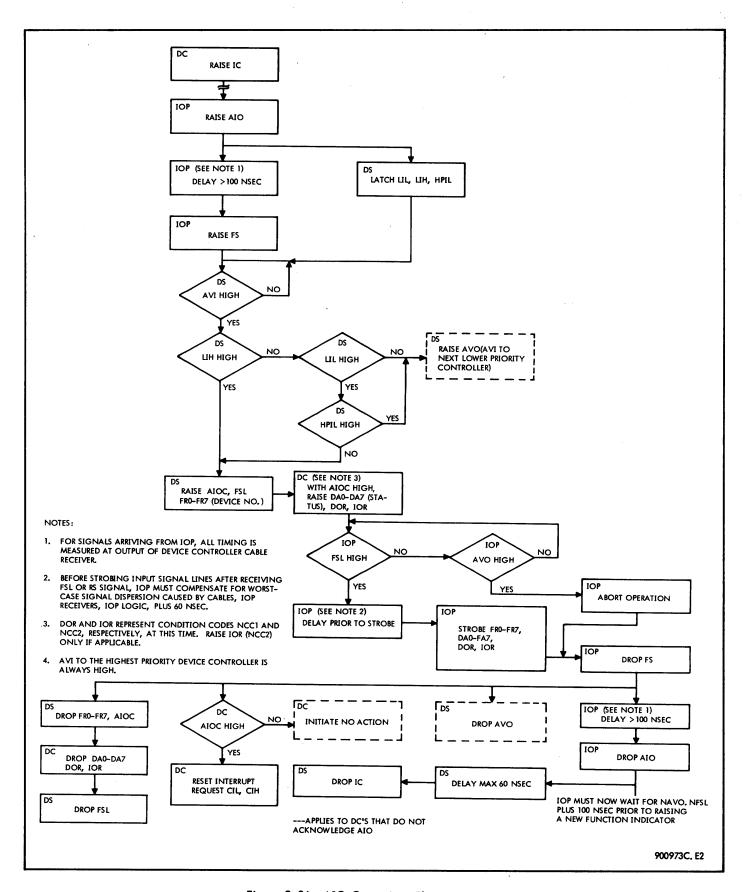

| 3-34          | SIO, HIO, TIO, and TDV, Flow Diagram                             | 3-58          |

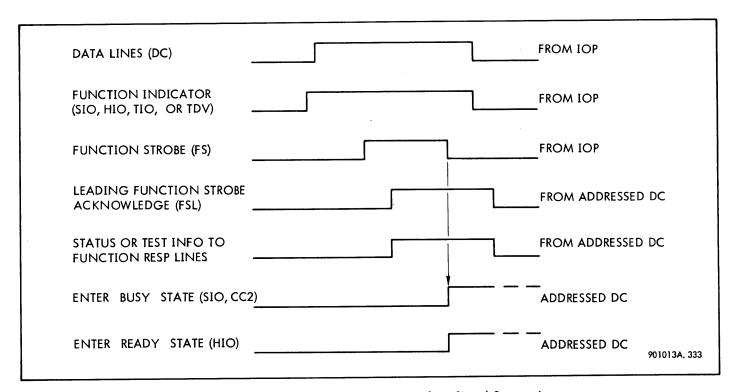

| 3-35          | SIO, HIO, TIO, and TDV Interface Signal Sequencing               | 3-60          |

| 3-36          | AIO Operation, Flow Diagram                                      | 3-61          |

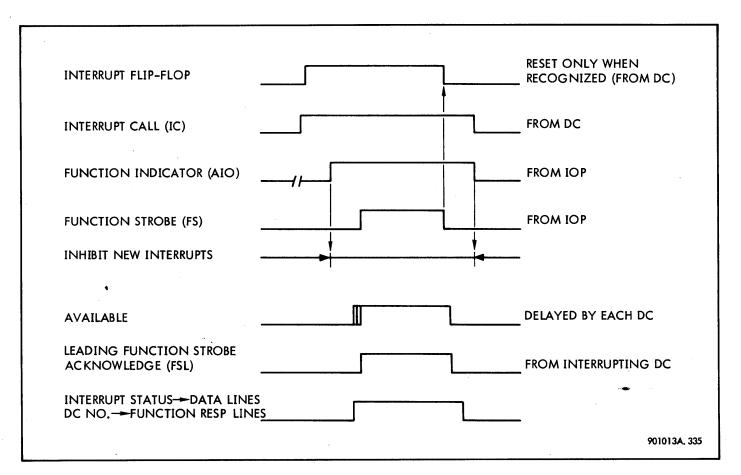

| 3-37          | AIO Interface Signal Sequencing                                  | 3-62          |

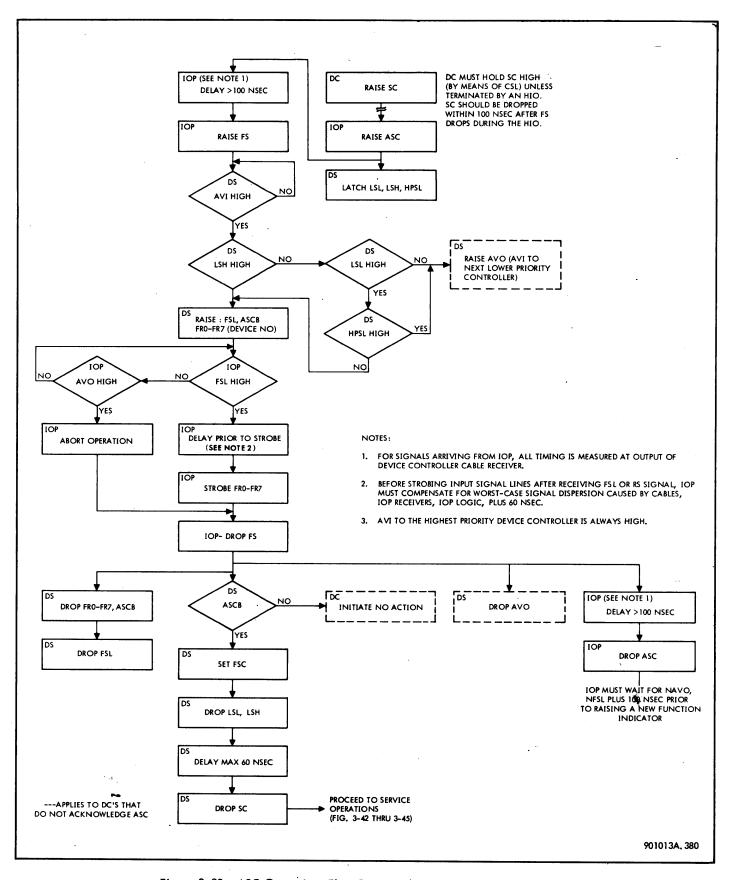

| 3-38          | ASC Operation, Flow Diagram (Prior to Service Connection)        | 3-63          |

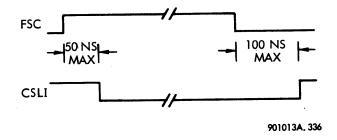

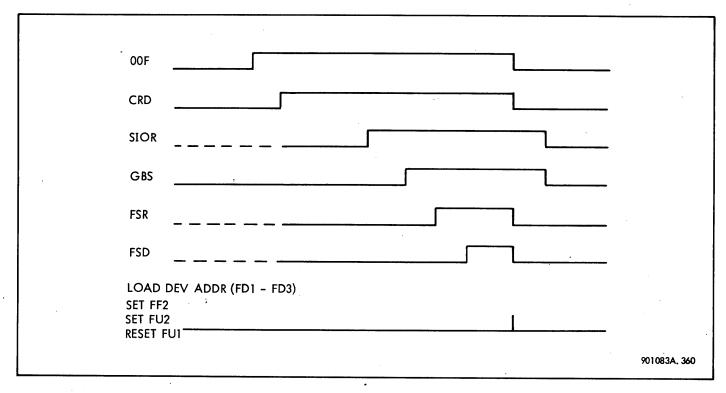

| 3-39          | FSC Interface Signal Sequencing                                  | 3-65          |

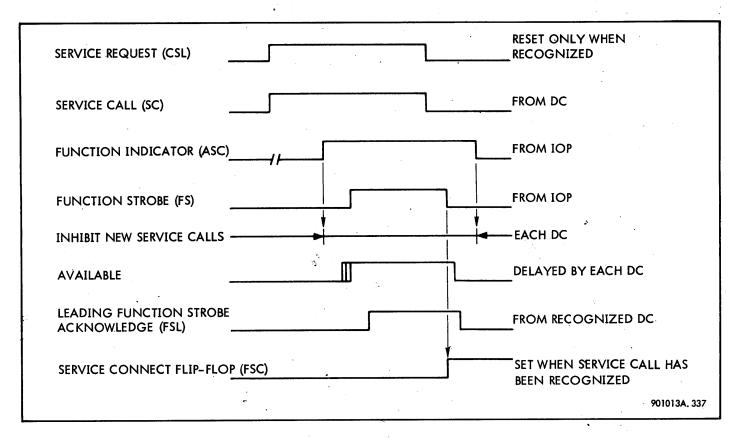

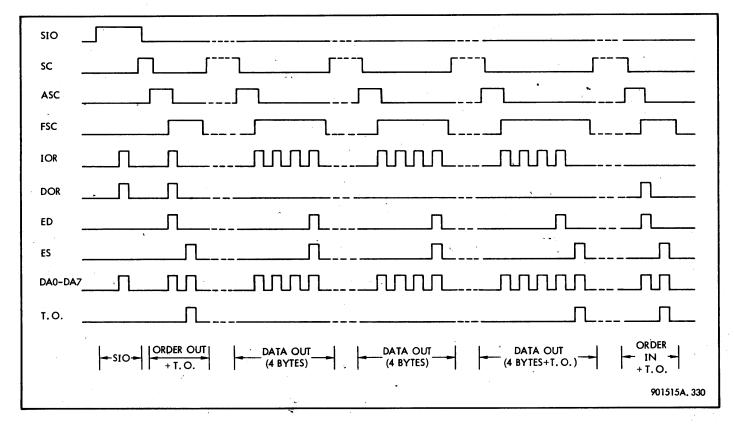

| 3-40          | Service Cycles, Timing Diagram                                   | 3-65          |

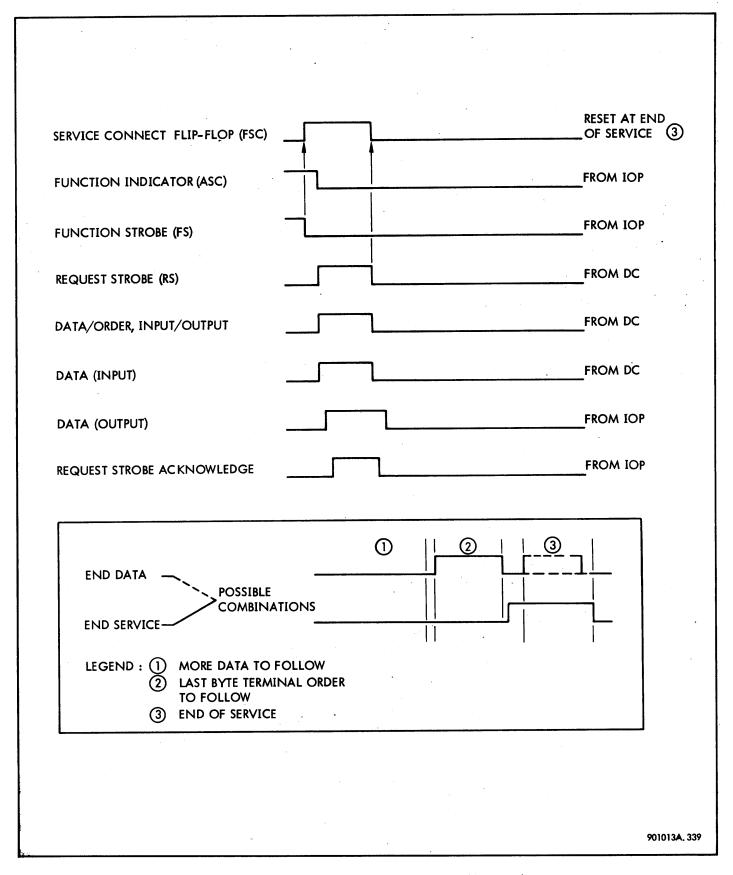

| 3-41          | Service Cycle, Timing Sequence (One Byte)                        | 3-66          |

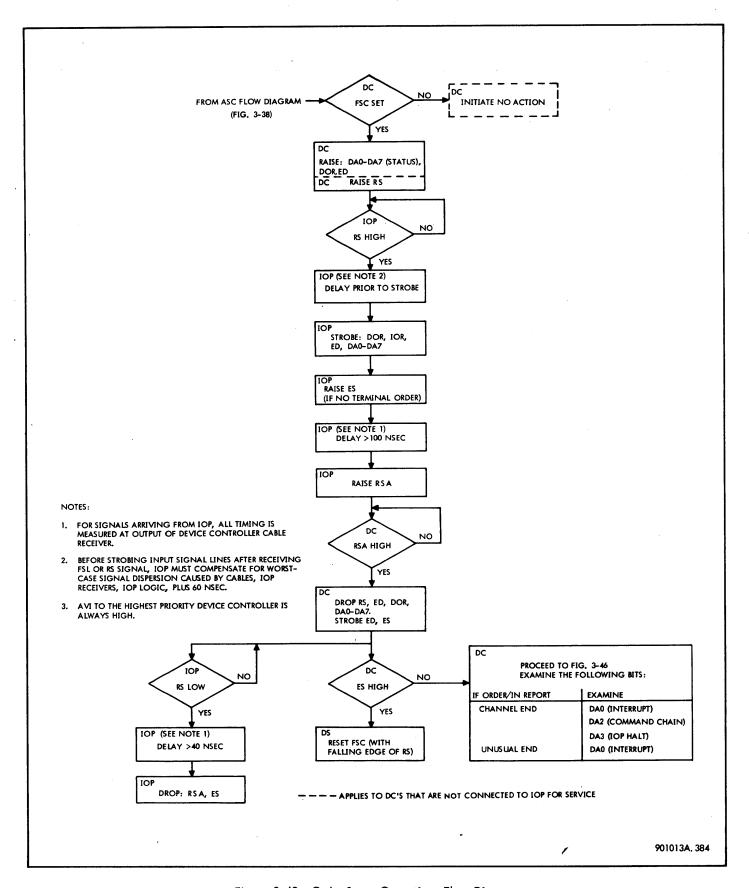

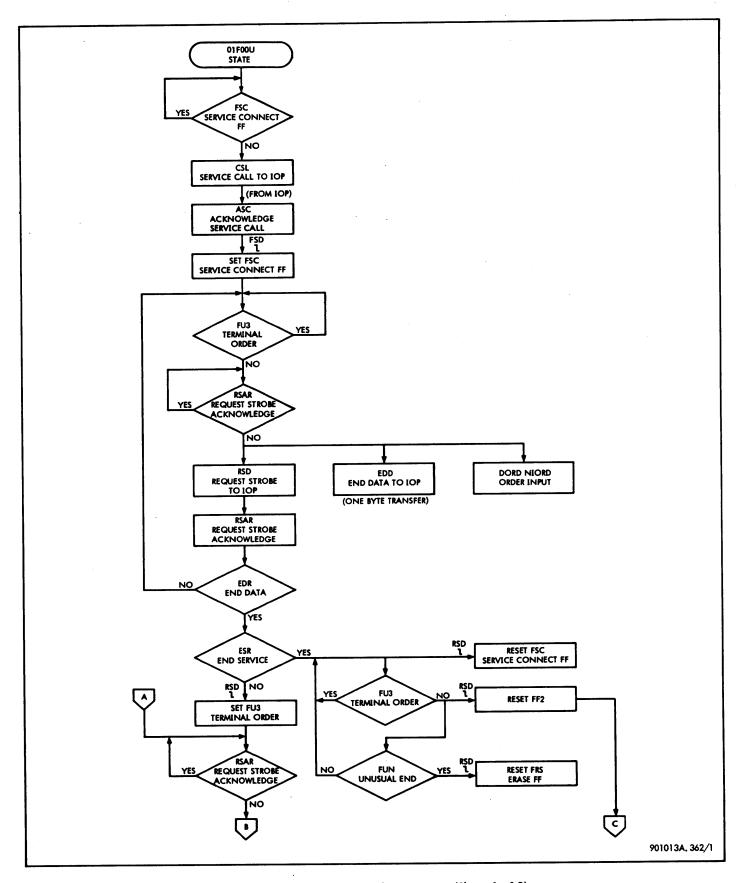

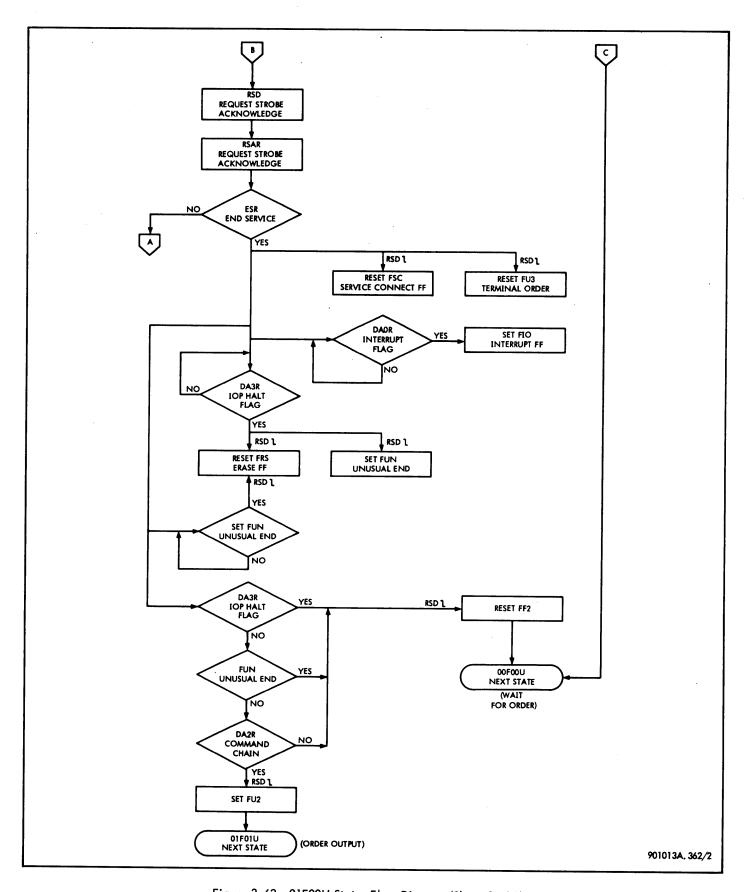

| 3-42          | Order Input Operation, Flow Diagram                              | 3-67          |

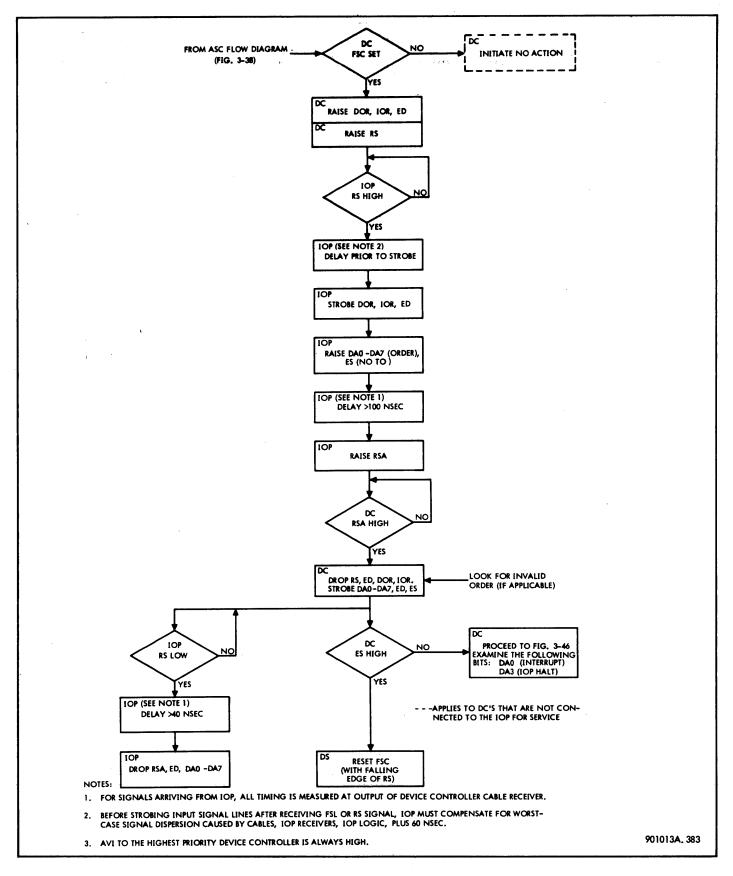

| 3-43          | Order Output Operation, Flow Diagram                             | 3-68          |

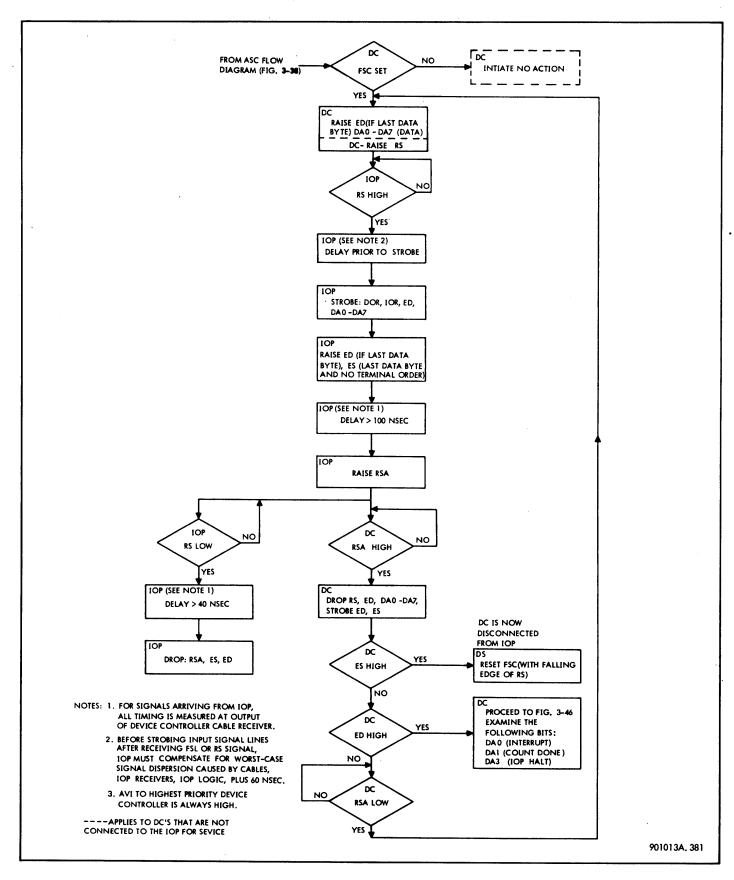

| 3-44          | Data Input Operation, Flow Diagram                               | 3-69          |

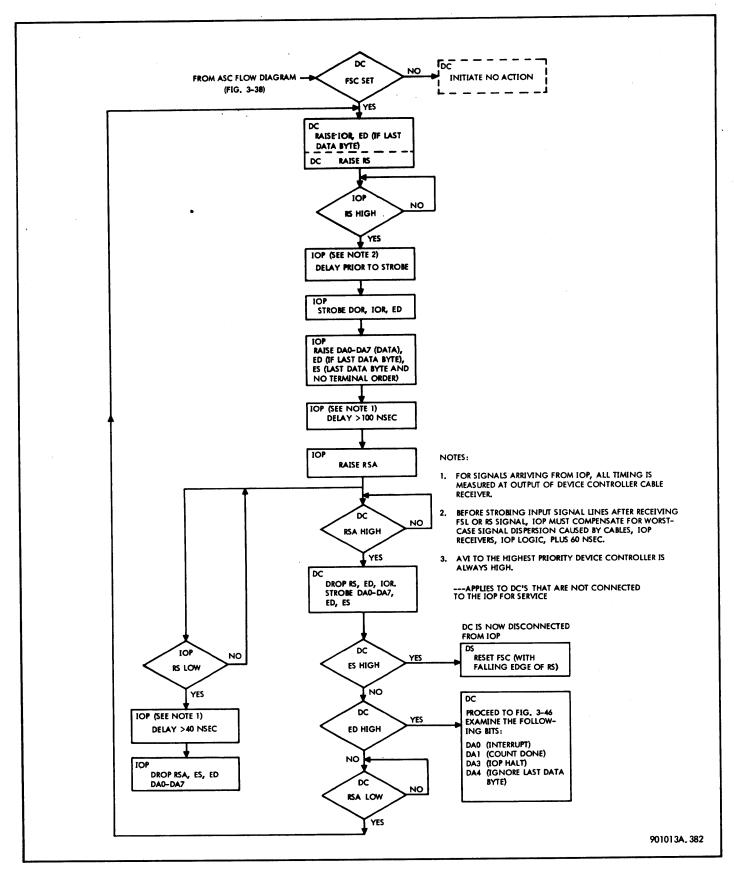

| 3-45          | Data Output Operation, Flow Diagram                              | 3- <i>7</i> 0 |

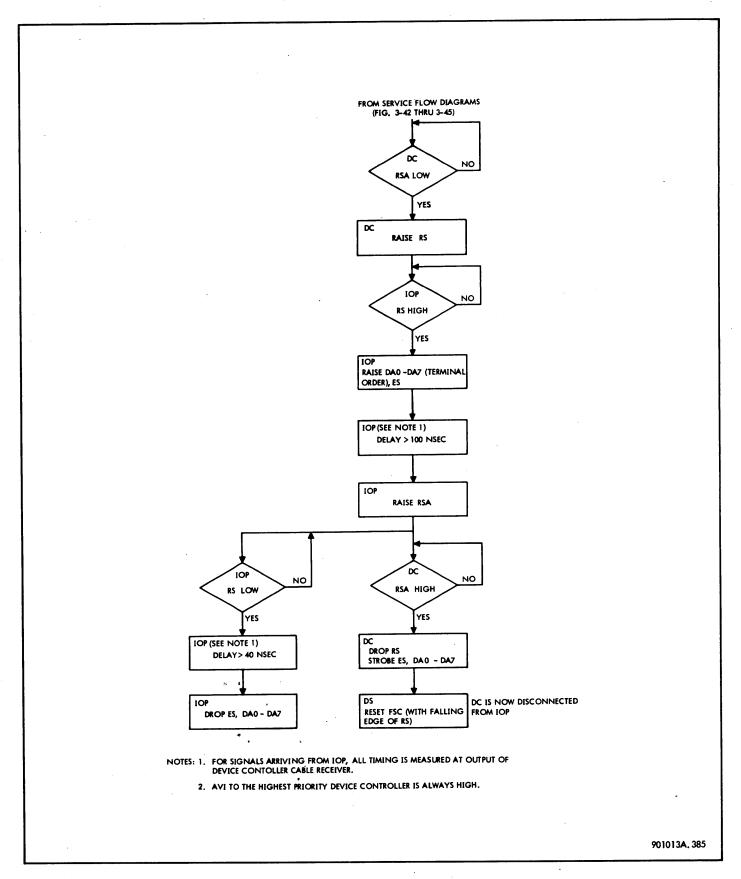

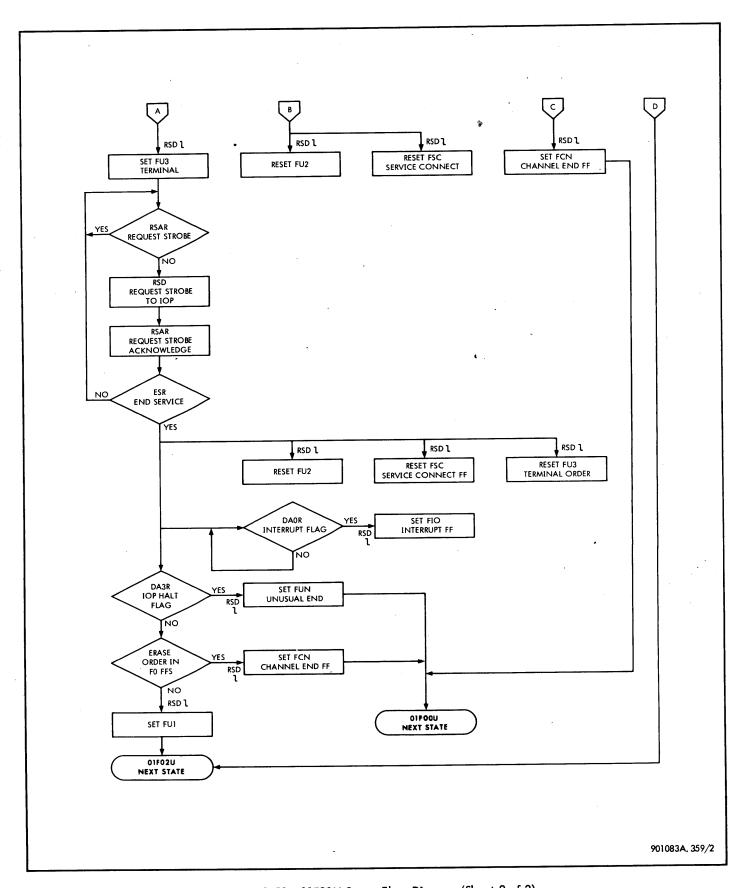

| 3-46          | Terminal Order Operation, Flow Diagram                           | 3-72          |

| 3-47          | Magnetic Tape Controller States, Flow Diagram                    | 3-73          |

| 3-48          | SIO Operation, Flow Diagram                                      | 3-74          |

| 3-49          | 00F00U State, Timing Diagram                                     | 3 <i>-</i> 75 |

| 3-50          | 01F01U State, Flow Diagram                                       | 3-77          |

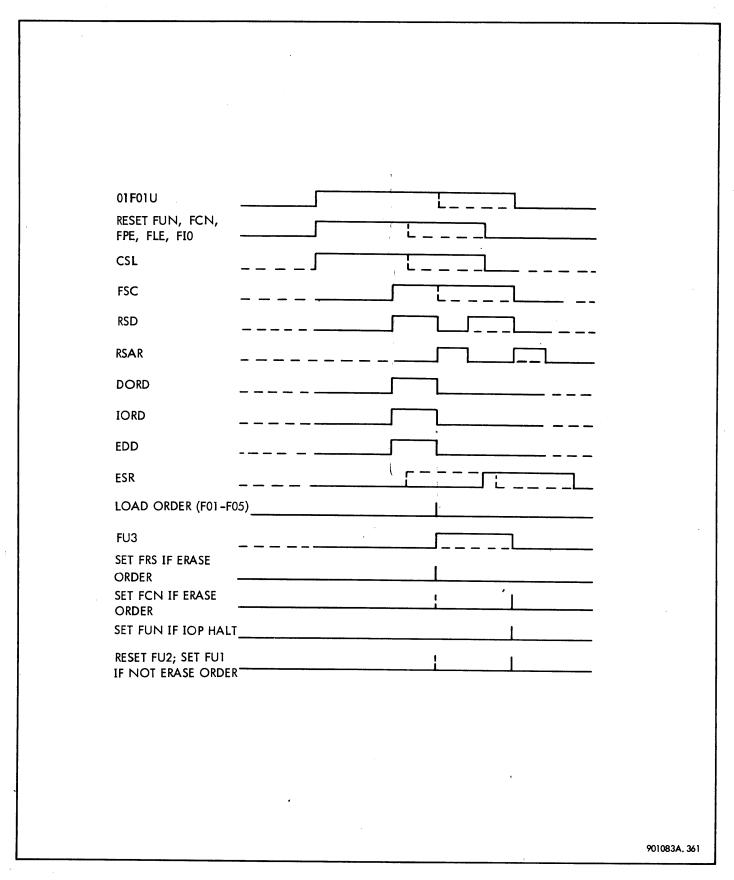

| 3-51          | 01F01U State, Timing Diagram                                     | 3-81          |

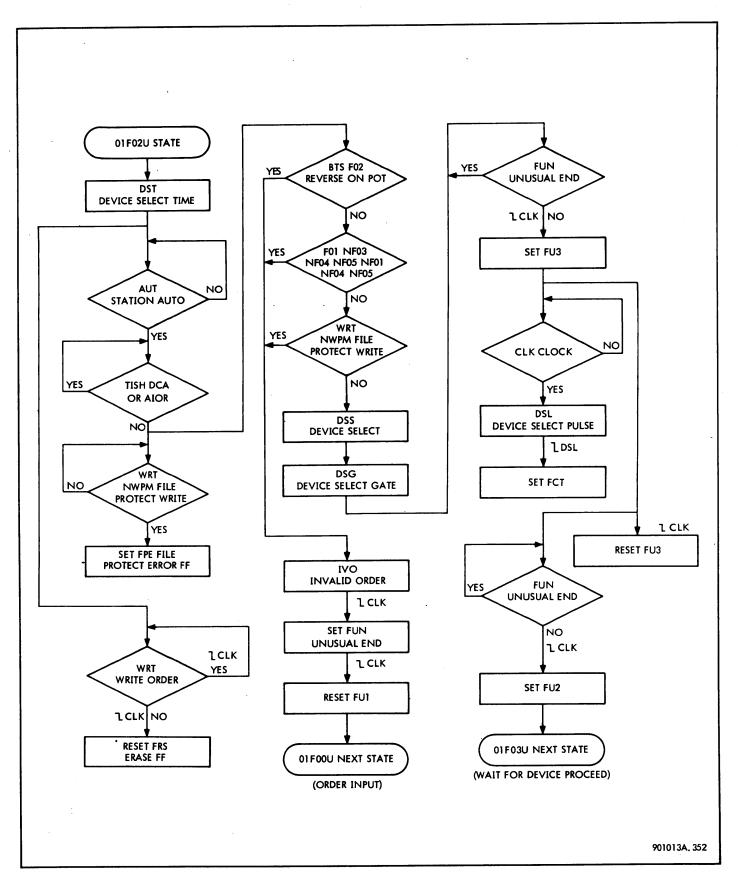

| 3-52          | 01F02U State, Flow Diagram                                       | 3-82          |

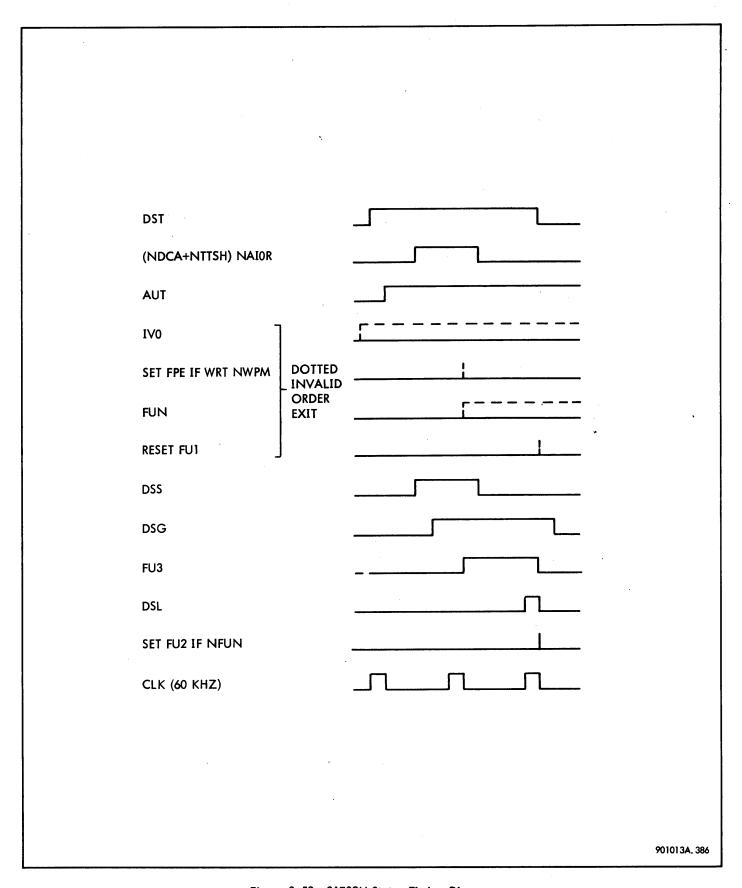

| 3-53          | 01F02U State, Timing Diagram                                     | 3-84          |

| 3-54          | 01F03U State, Flow Diagram                                       | 3-85          |

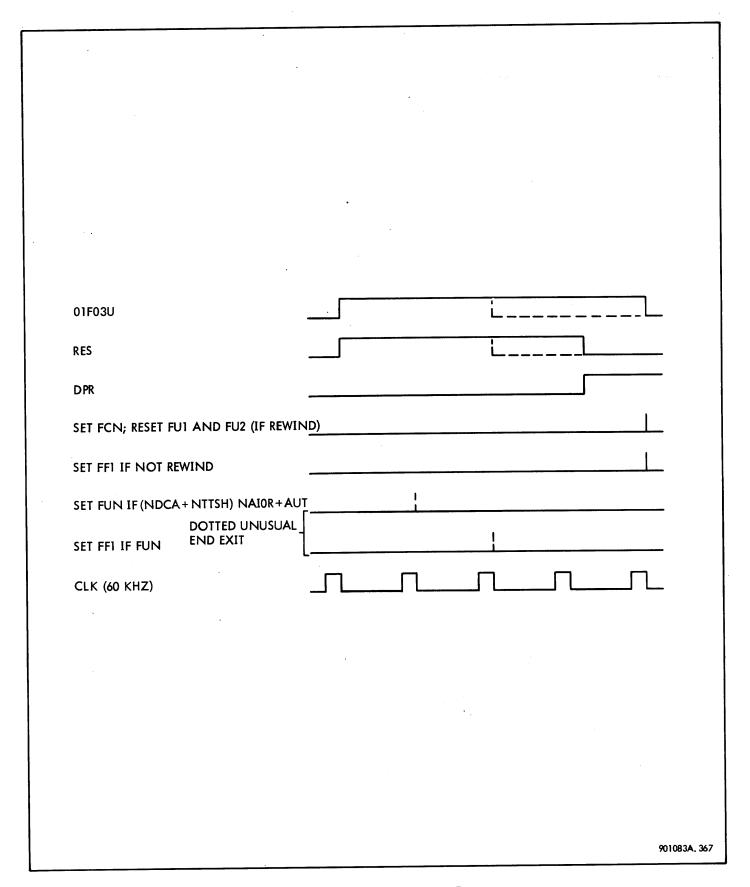

| 3-55          | 01F03U State, Timing Diagram                                     | 3-86          |

| 3-56          | 03F03U-02U State, Flow Diagram                                   | 3-87          |

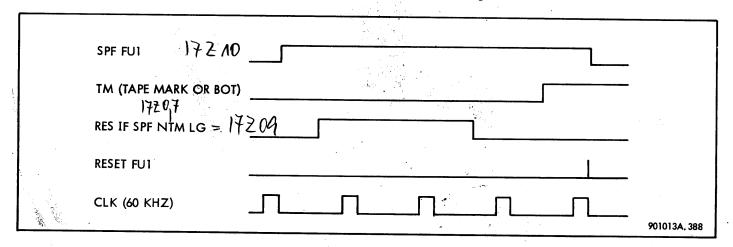

| 3-57          | 03F03U State (Space File), Timing Diagram                        | 3-87          |

| 3-58          | 03F03U State (Space Record), Timing Diagram                      | 3-89          |

| 3-59          | 03F01U State, Flow Diagram                                       | 3-89          |

| 3-60          | 03F01U State, Timing Diagram                                     | 3-90          |

| 3-61          | 03F00U State, Flow Diagram                                       | 3-91          |

| 3-62          | 01F00U State, Flow Diagram                                       | 3-92          |

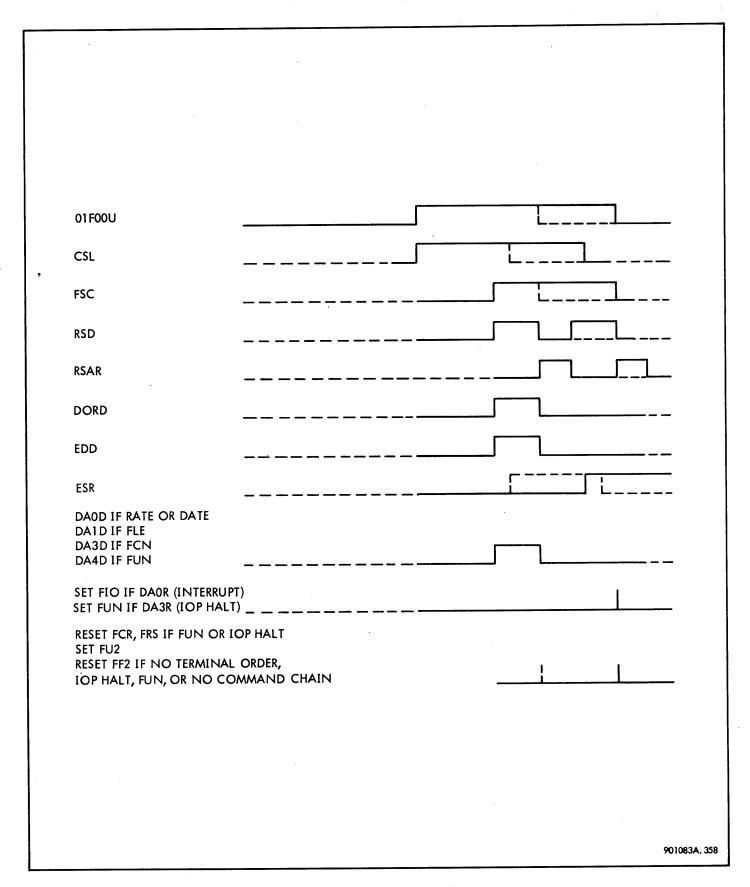

| 3-63          | 01F00U State, Timing Diagram                                     | 3-94          |

| 3-64          | Read/Write Operation, Flow Diagram                               | 3-96          |

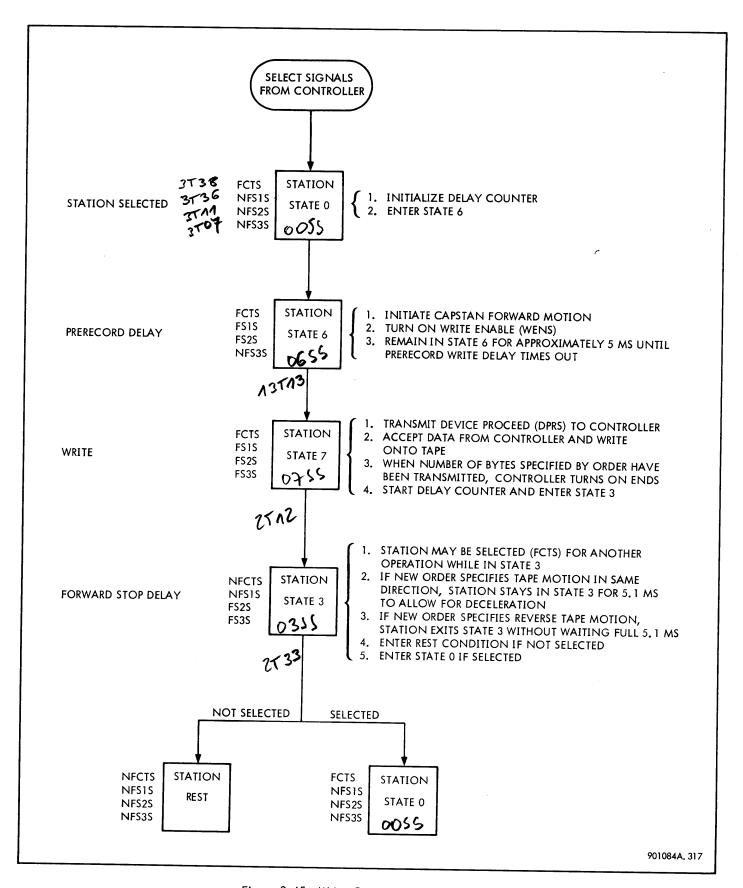

| 3 <b>-</b> 65 | Write Operation, Flow Diagram                                    | 3-97          |

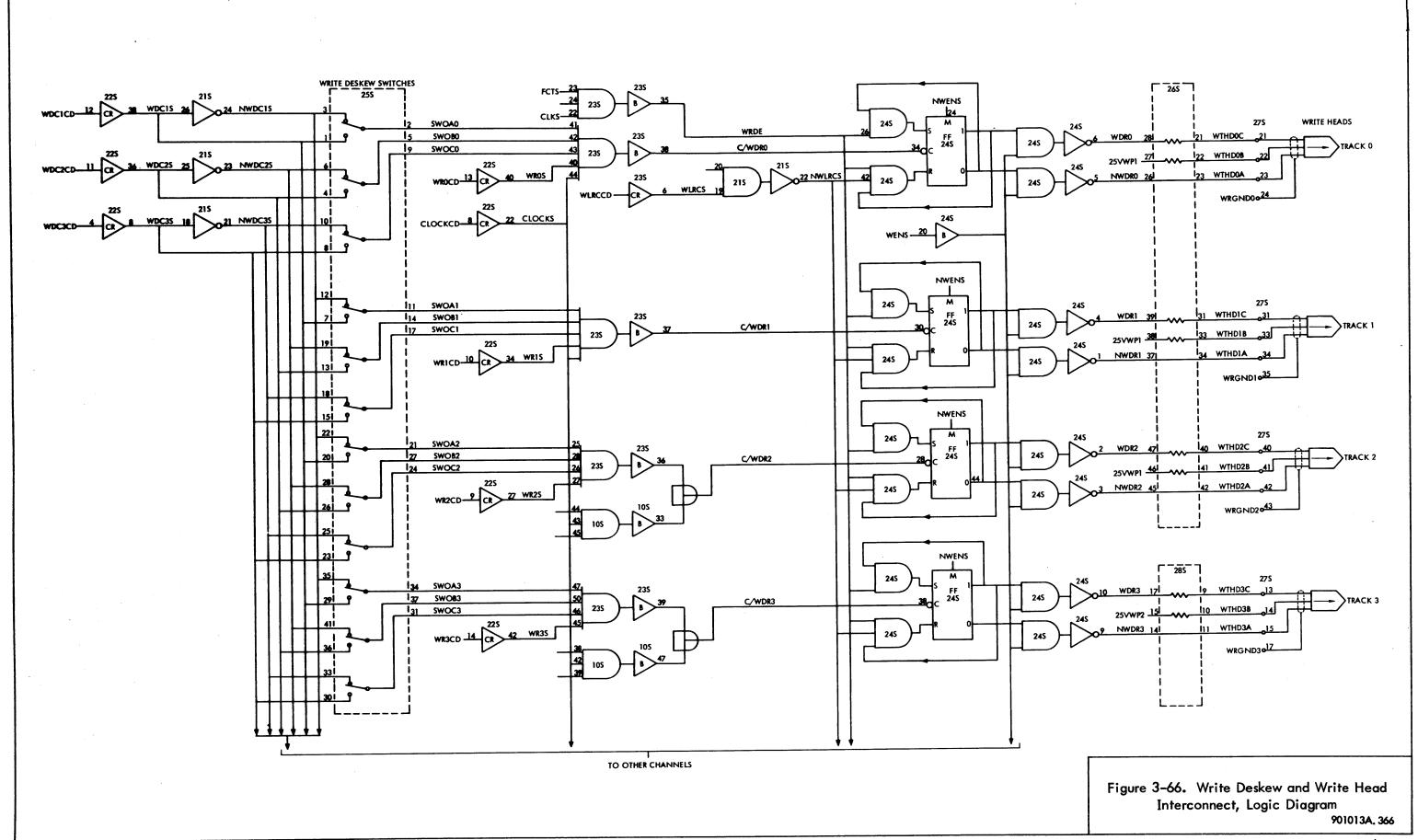

| 3-66          | Write Deskew and Write Head Interconnect, Logic Diagram          | 3-99          |

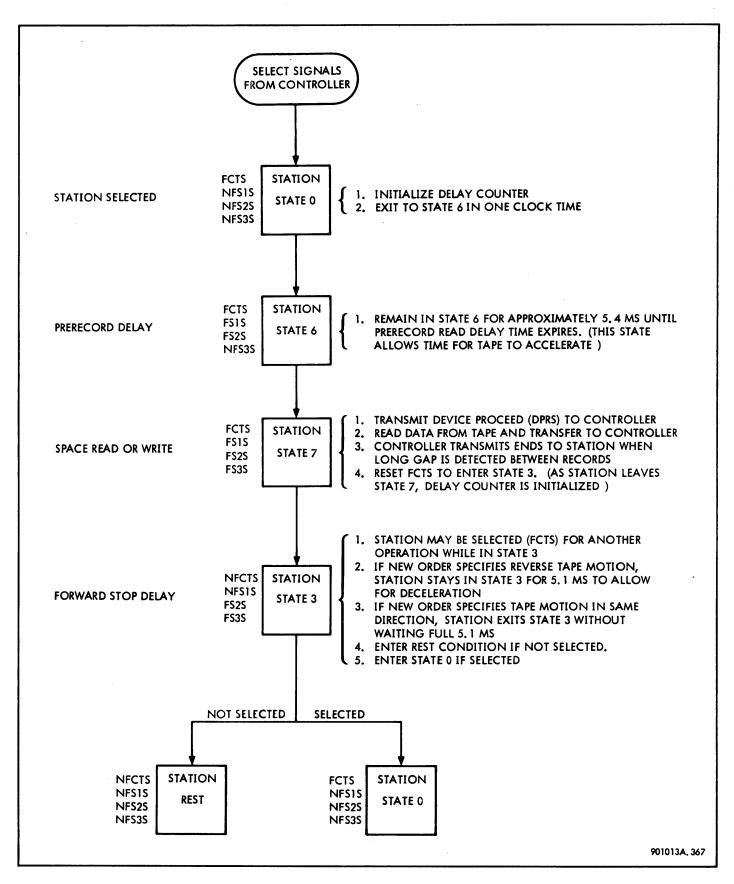

| 3-67          | Read Operation, Flow Diagram                                     | 3-102         |

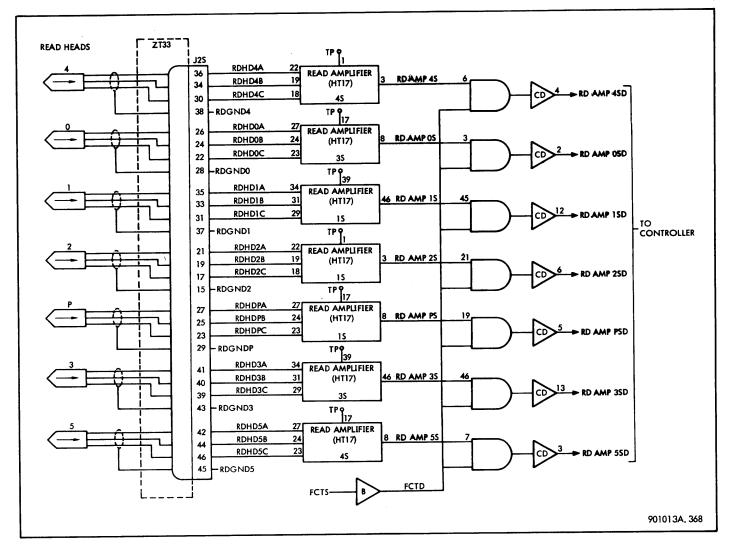

| 3-68          | Read Head Interconnect, Logic Diagram                            | 3-104         |

| 3-69          | Controller, Block Diagram                                        | 3-106         |

| 3 <i>-7</i> 0 | Memory Access (Controller and Station), Timing Diagram           | 3-109         |

| 3-71          | Write Start (800 bpi), Timing Diagram                            | 3-112         |

| 3-72          | Write Operation (800 bpi), Timing Diagram                        | 3-115         |

| 3-73          | Write Finish BIN or BCD Mode (800 bpi), Timing Diagram           | 3-118         |

| 3-74          | Write Finish Pack Mode (800 bpi), Timing Diagram                 | 3-120         |

| 3-75          | Write Tape Mark (800 bpi), Timing Diagram                        | 3-121         |

| 3-76          | Read Start, Timing Diagram                                       | 3-122         |

| 3-77          | Read Operation, Timing Diagram                                   | 3-127         |

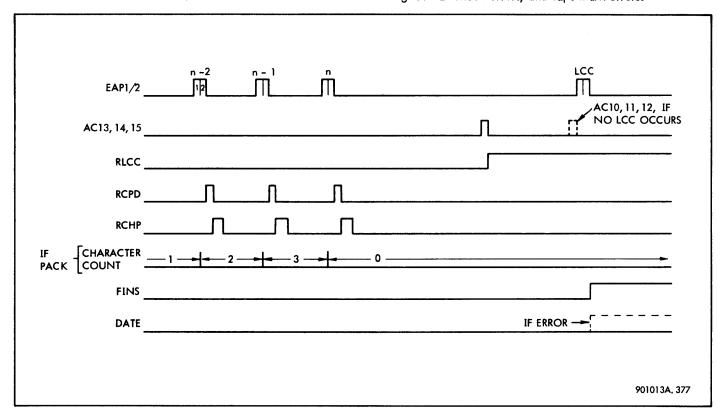

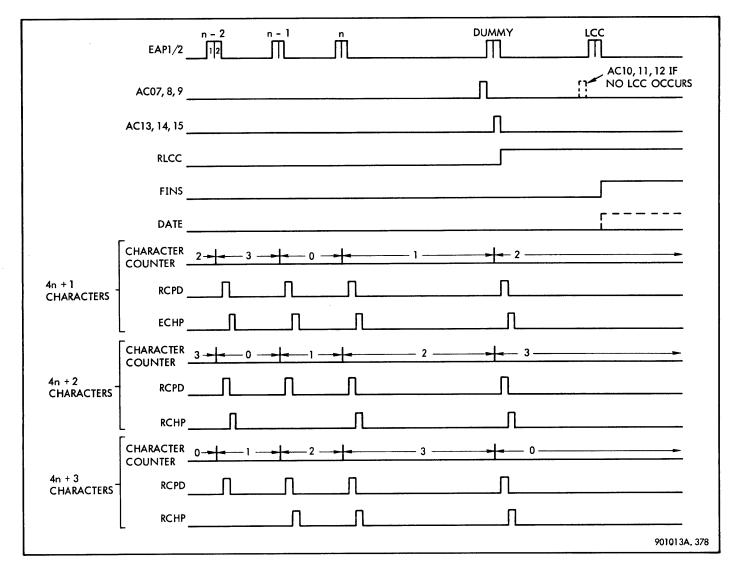

| 3 <i>-7</i> 8 | Read End (BIN, BCD, or Pack, 4n Characters Read), Timing Diagram | 3-131         |

| 3-79          | Read End (Pack, Not 4n Characters Read), Timing Diagram          | 3-132         |

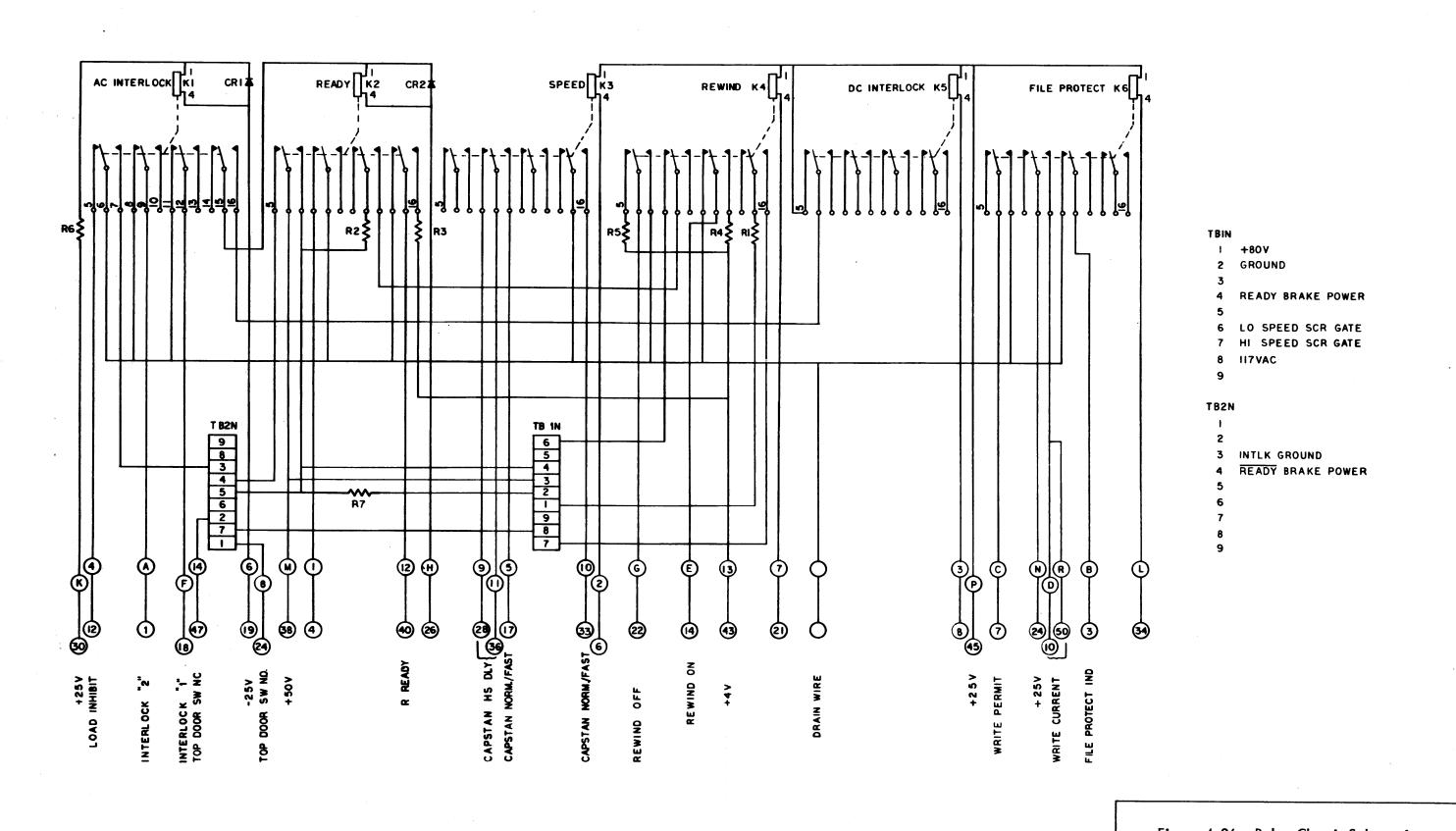

| 4-1           | Station Interconnection Diagram                                  | 4-3           |

| 4-2           | Magnetic Tape Station Wiring Diagram                             | 4-4           |

| 4-3           | Module Location Chart                                            | 4-5           |

| 4-4           | Waveforms, Capstan Speed Adjustments                             | 4-16          |

| 4-5           | Waveforms, Ramp Adjustment                                       | 4-17          |

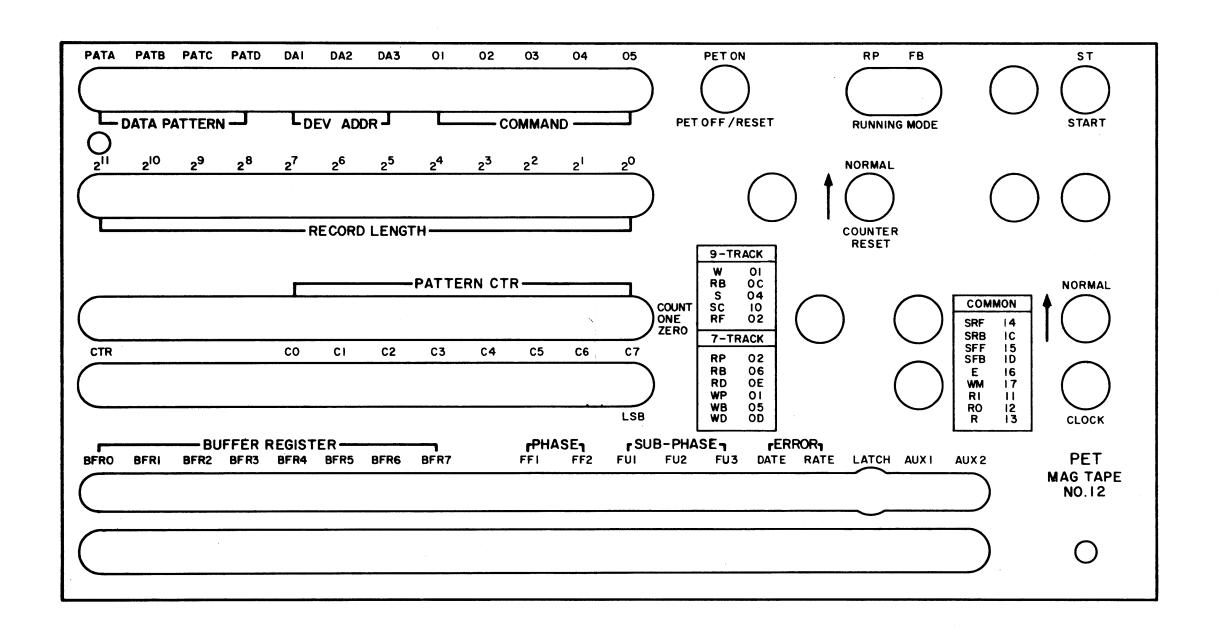

| 4-6           | PET Magnetic Tape Overlay No. 12                                 | 4-27          |

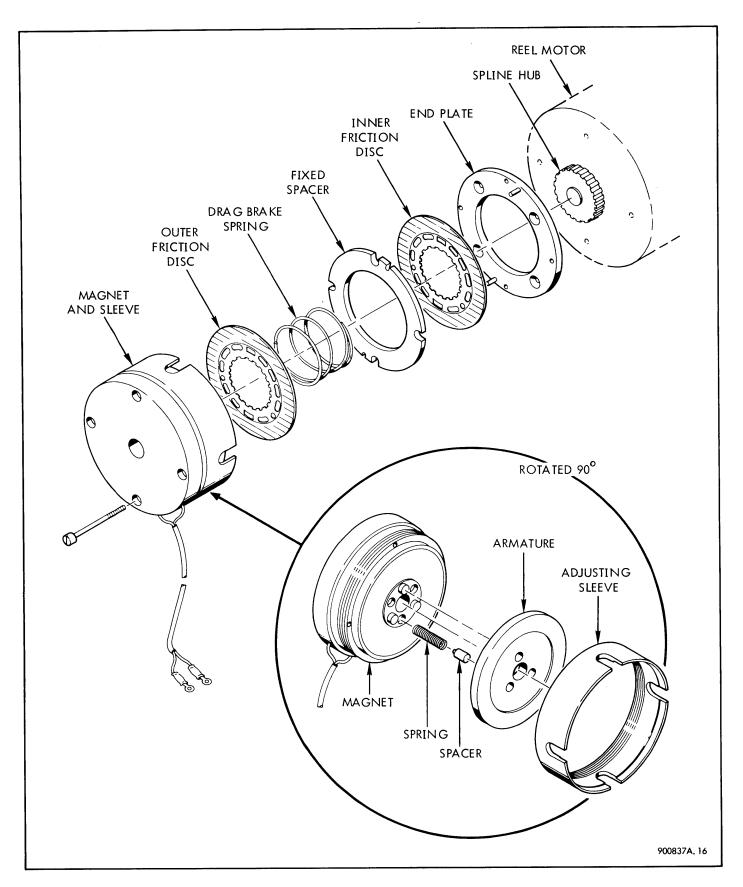

| 4-7           | Reel Motor Brake, Exploded View                                  | 4-33          |

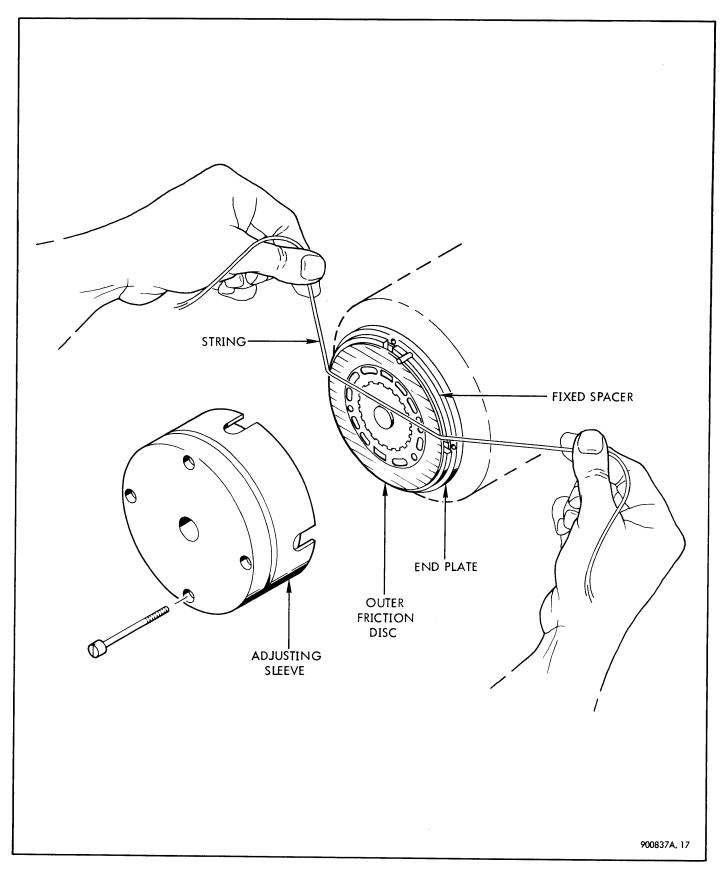

| 4-8           | Reel Motor Brake, Reassembly                                     | 4-34          |

| 4-9           | File Reel Hub                                                    | 4-35          |

### LIST OF ILLUSTRATIONS (Cont.)

| Figure | Title                                               | Page   |

|--------|-----------------------------------------------------|--------|

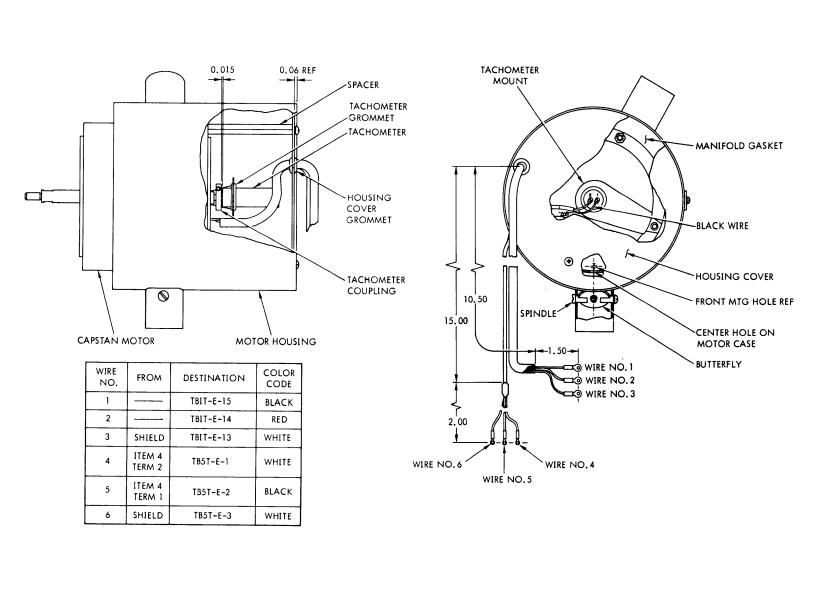

| 4-10   | Capstan Tachometer Mounting Position                | 4-38   |

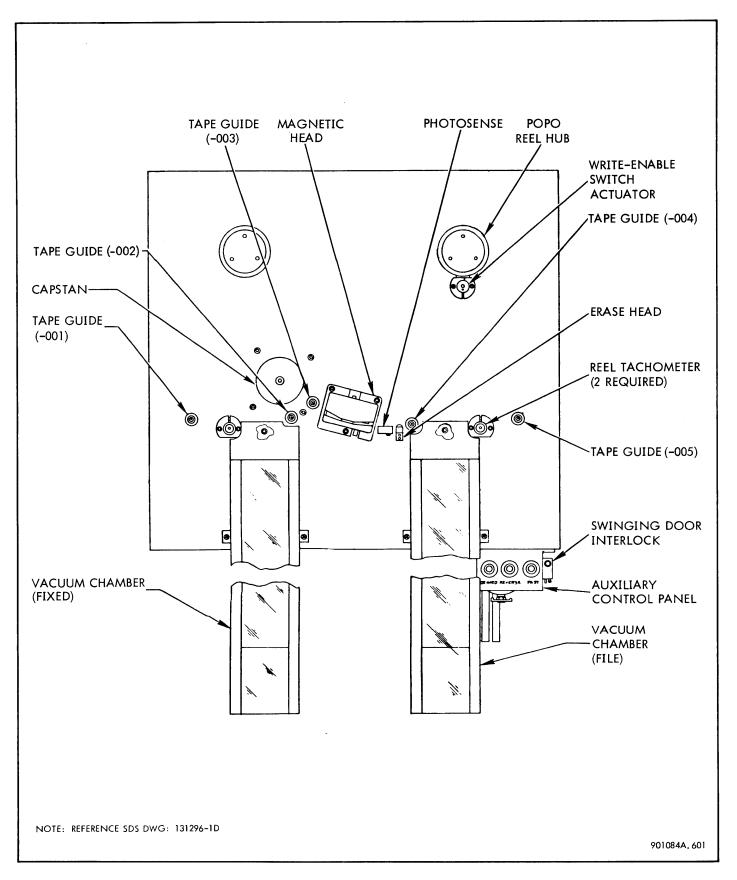

| 4-11   | Transport Front View                                | 4-41   |

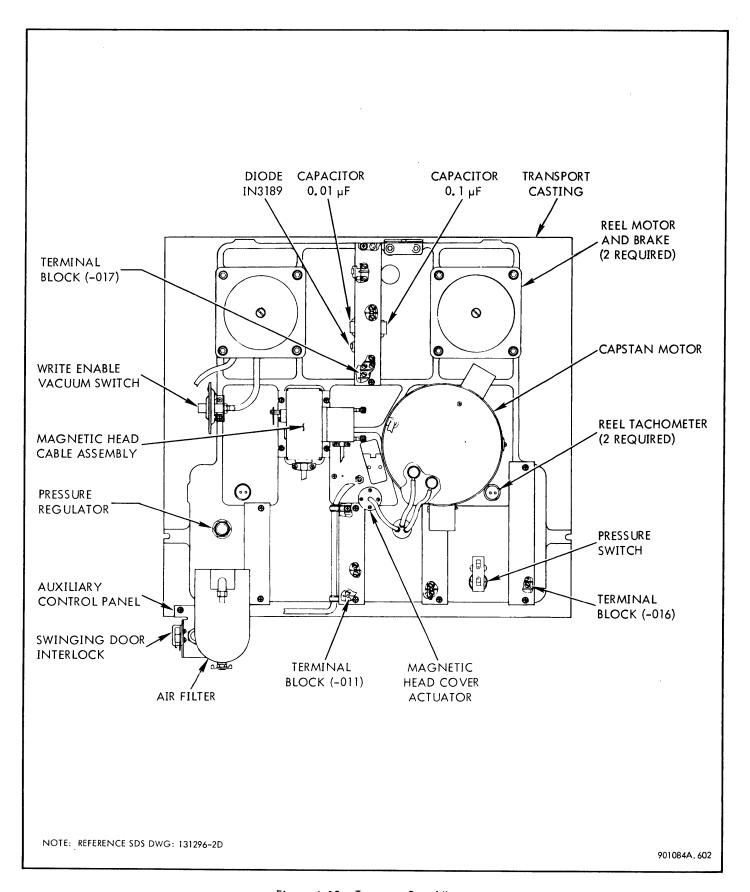

| 4-12   | Transport Rear View                                 | 4-42   |

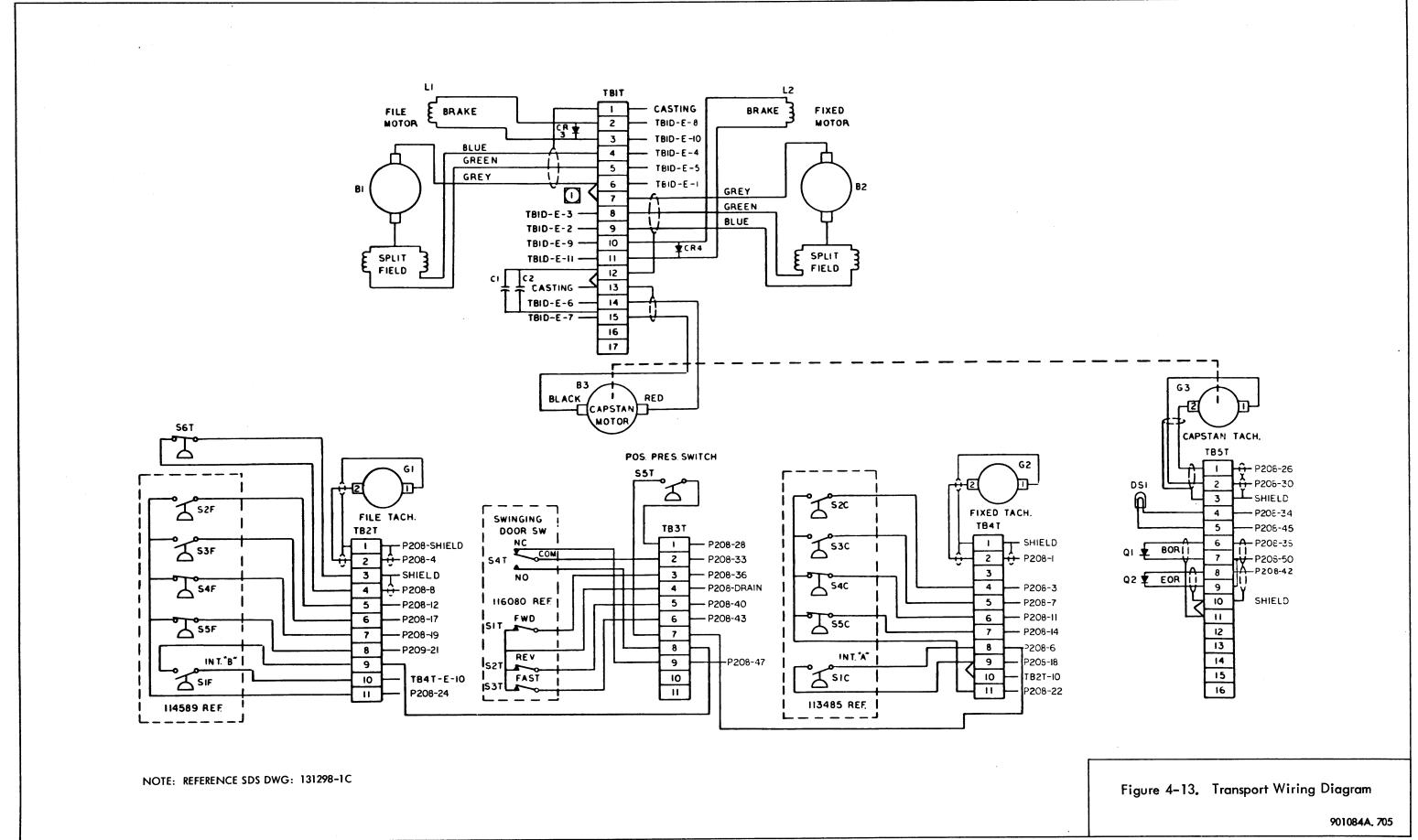

| 4-13   | Transport Wiring Diagram                            | 4-45   |

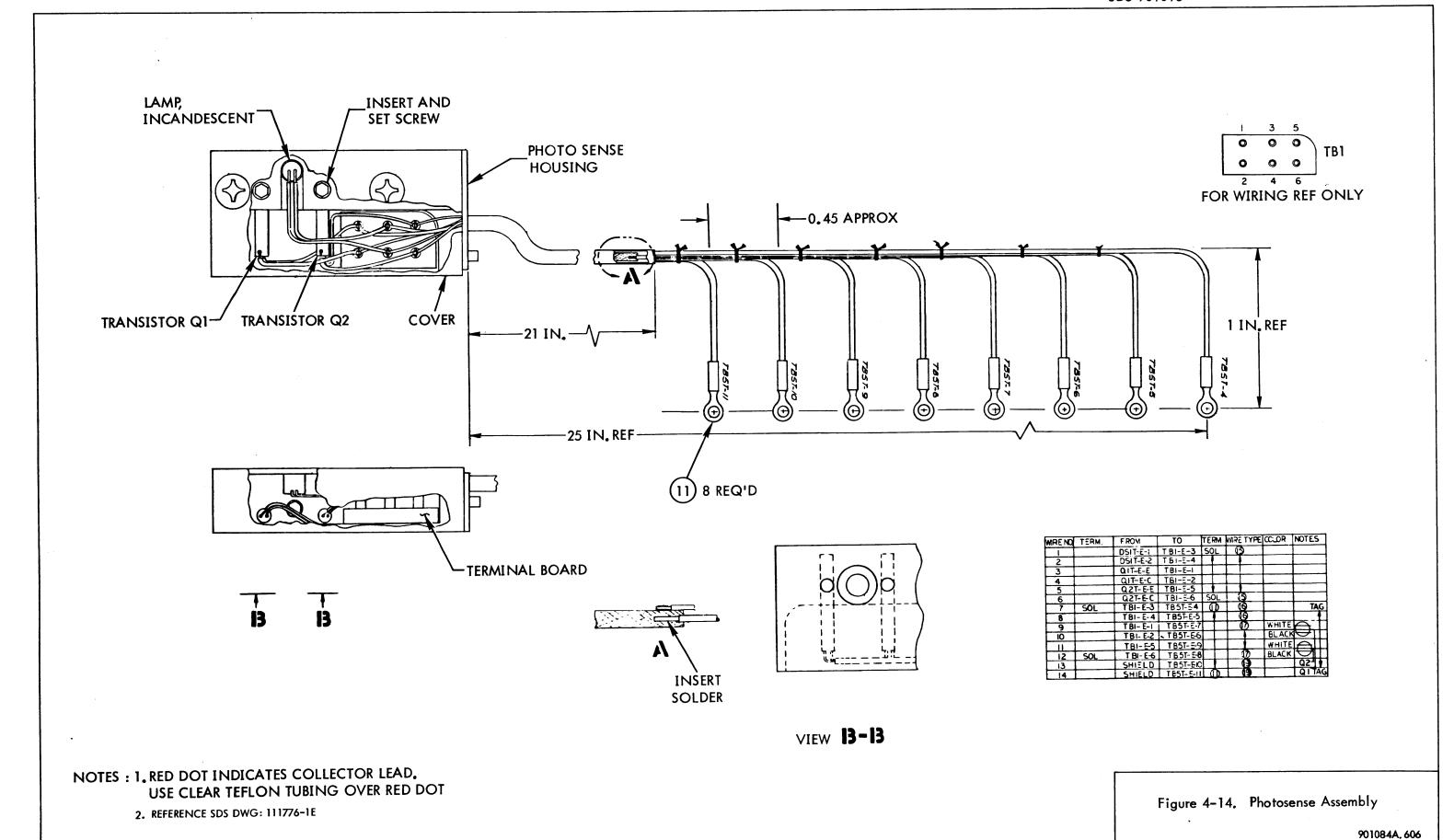

| 4-14   | Photosense Assembly                                 | 4-49   |

| 4-15   | Capstan Motor Assembly                              | 4-52   |

| 4-16   | Erase Head Assembly                                 | 4-53   |

| 4-17   | Read/Write Head Assembly                            | 4-54   |

| 4-18   | Auxiliary Control Panel Assembly                    | 4-56   |

| 4-19   | Reel Tachometer Assembly                            | 4-57   |

| 4-20   | Blower Shelf Assembly                               | 4-60   |

| 4-21   | Blower Shelf Schematic                              | 4-61   |

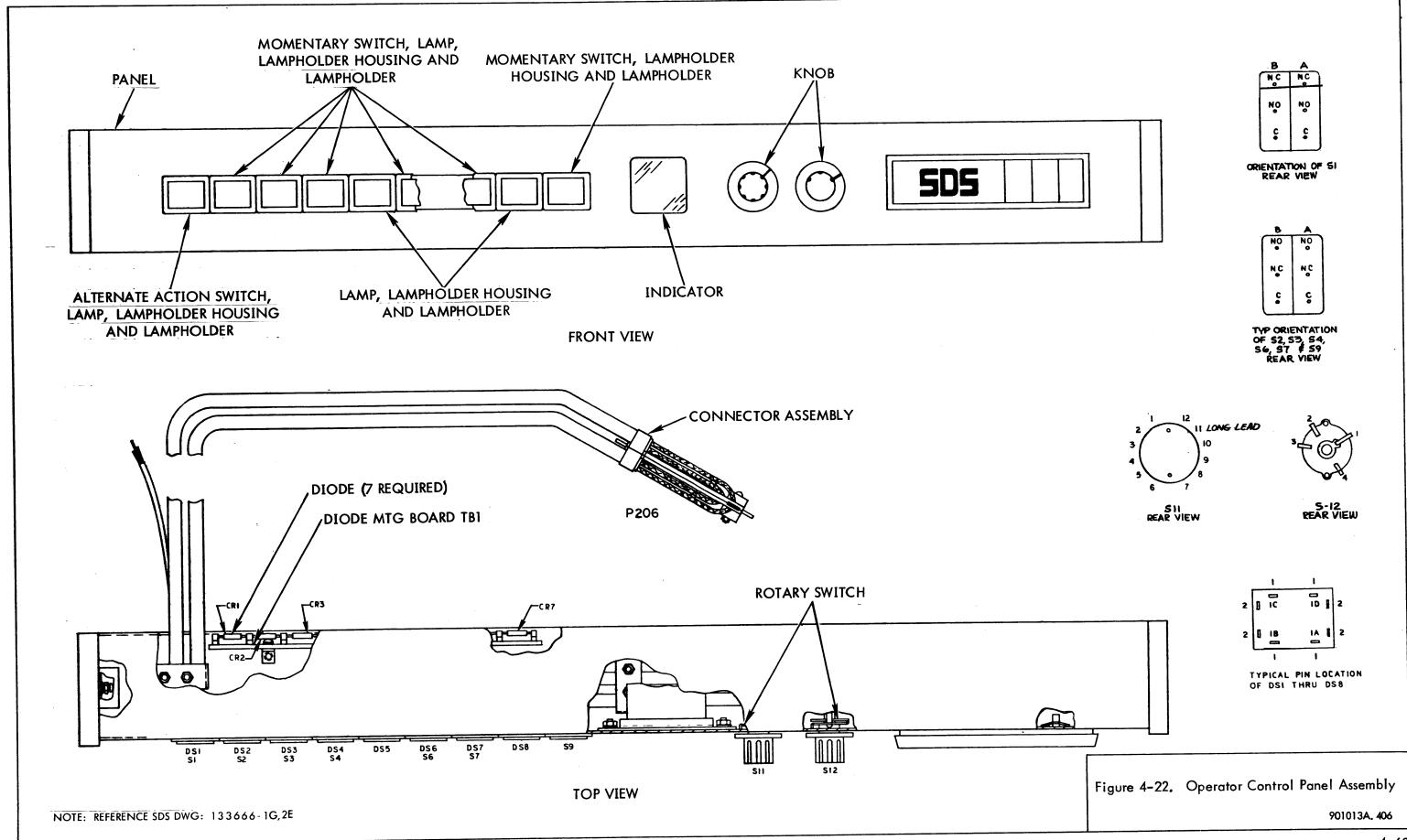

| 4-22   | Operator Control Panel Assembly                     | 4-63   |

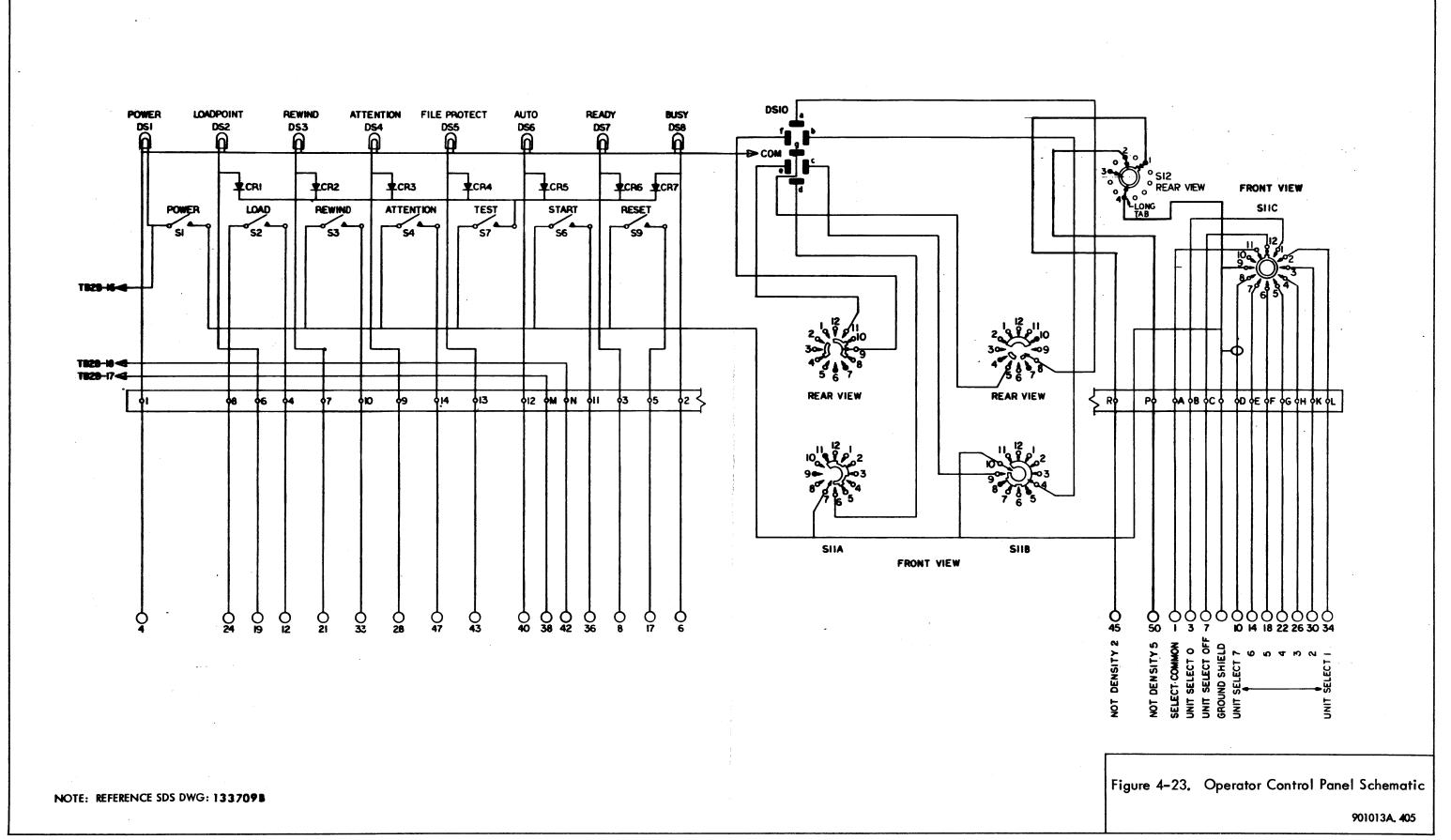

| 4-23   | Operator Control Panel Schematic                    | 4-64   |

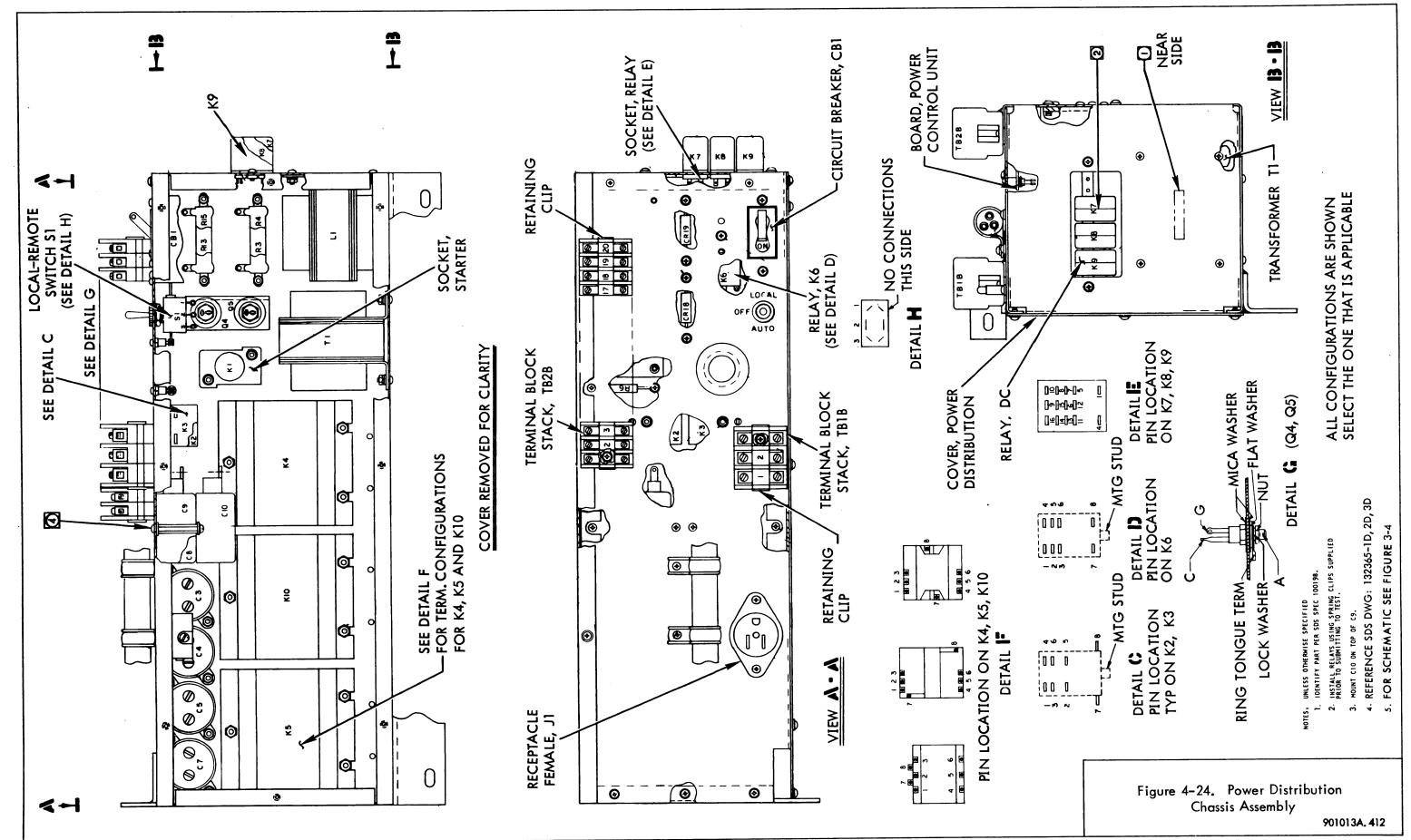

| 4-24   | Power Distribution Chassis Assembly                 | 4-67   |

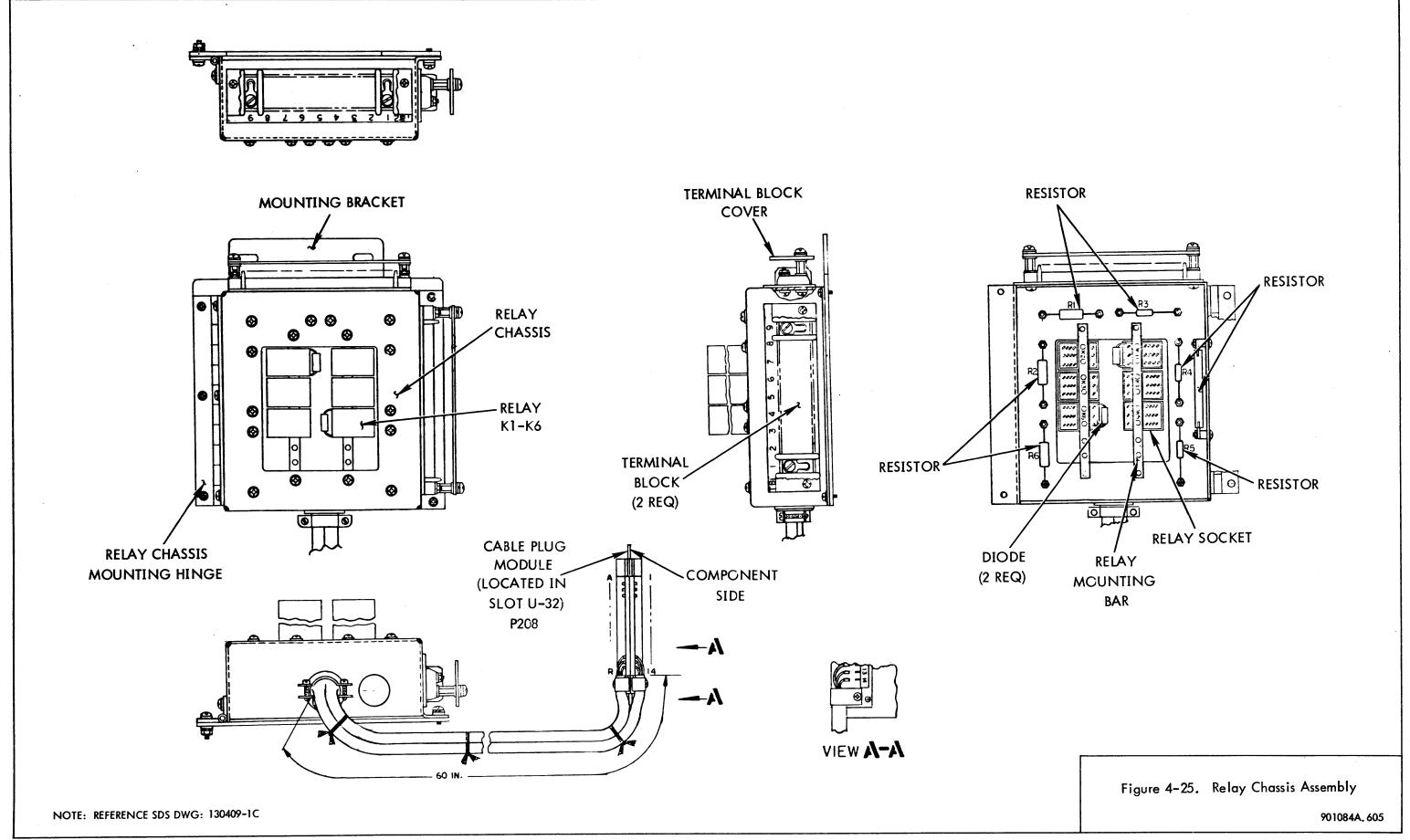

| 4-25   | Relay Chassis Assembly                              | 4-71   |

| 4-26   | Relay Chassis Schematic                             | 4-72   |

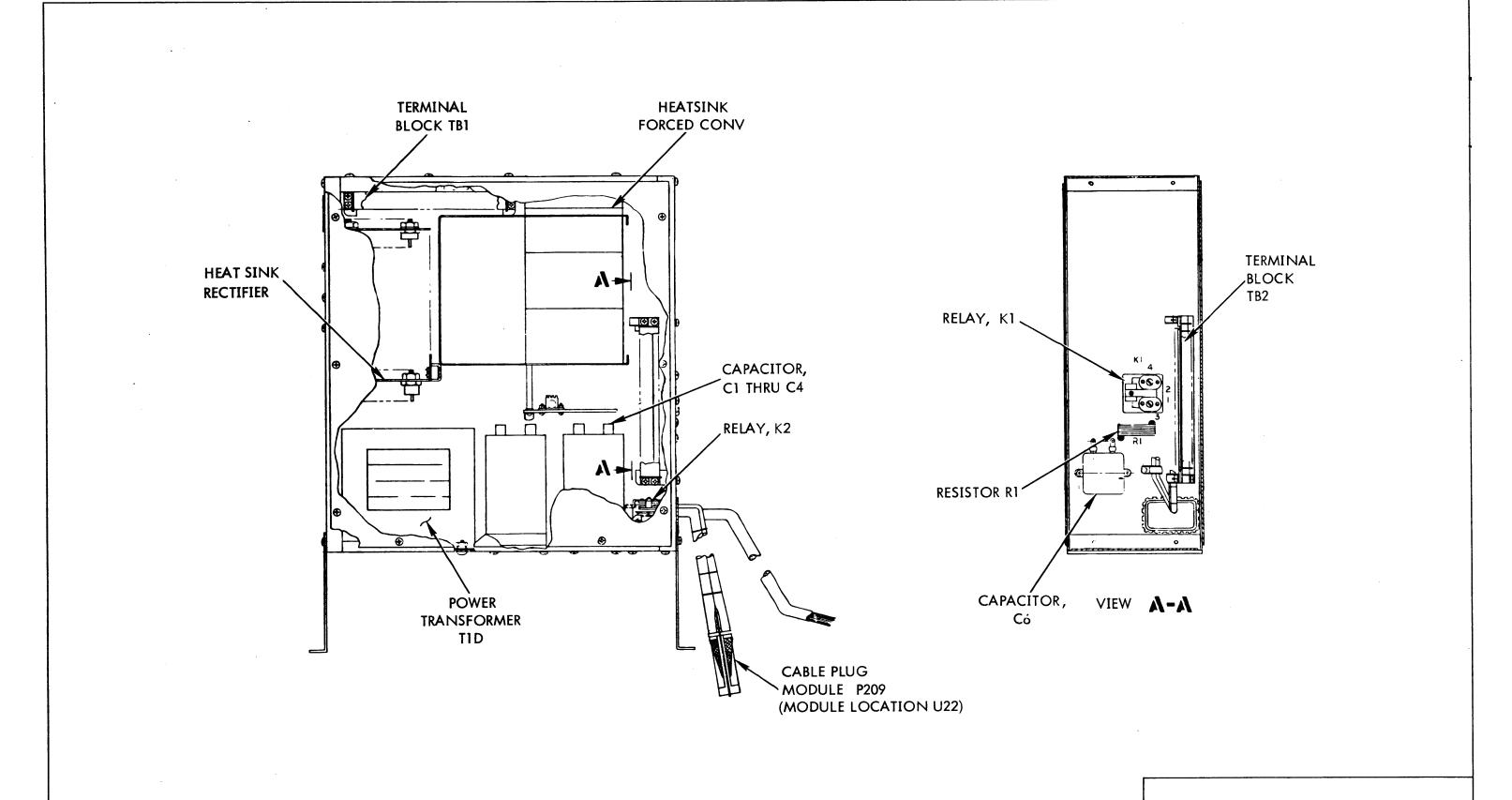

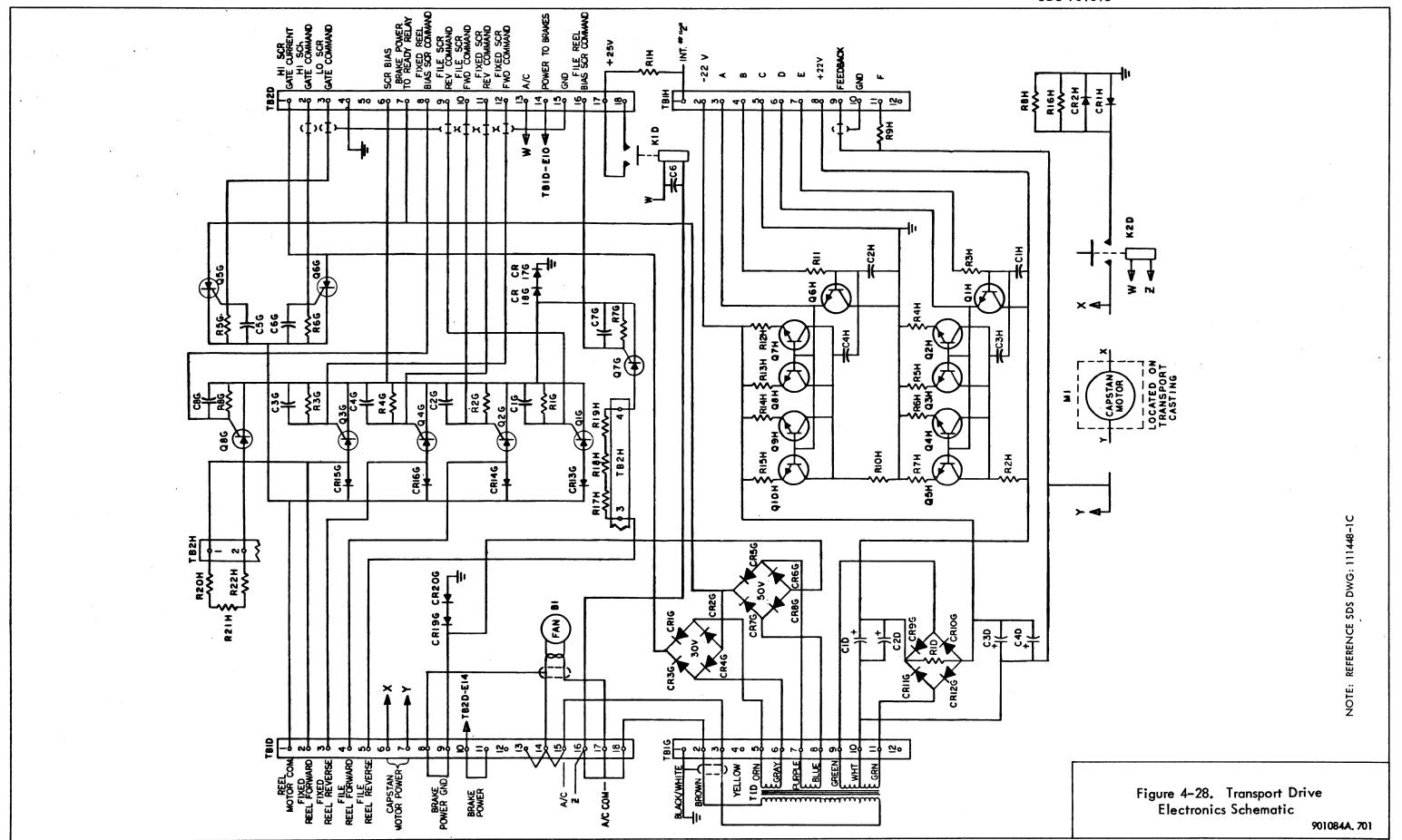

| 4-27   | Transport Drive Electronics Assembly                | 4 - 75 |

| 4-28   | Transport Drive Electronics Schematic               | 4-76   |

|        |                                                     |        |

|        | LIST OF TABLES                                      |        |

| Table  | Title                                               | Page   |

| 1-1    | General Requirements                                | 1-6    |

| 1-2    | Parameter Definitions and Specifications            | 1-6    |

| 2-1    | Operator Control Panel Switches and Indicators      | 2-2    |

| 2-2    | Auxiliary Control Panel Switches                    | 2-4    |

| 2-3    | Power Distribution Chassis Switches                 | 2-5    |

| 2-4    | Manually Operated Interlock Switches                | 2-5    |

| 2-5    | Status Responses, SIO, HIO, and TIO Instructions    | 2-9    |

| 2-6    | Status Responses, TDV Instruction                   | 2-10   |

| 2-7    | Status Responses, AIO Instruction                   | 2-10   |

| 2-8    | Input/Output Order Bytes                            | 2-11   |

| 3-1    | BCDIC to EBCDIC Conversion                          | 3-4    |

| 3-2    | Delay Count Register Data                           | 3-34   |

| 3-3    | State Counter Data                                  | 3-38   |

| 3-4    | Subcontroller Connector/Cable/Module Identification | 3-47   |

| 3-5    | Subcontroller Interface                             | 3-51   |

| 3-6    | Transport Modes                                     | 3-54   |

| 3-7    | Magnetic Tape System Interface Signals              | 3-54   |

| 3-8    | Buffer Register Status During Write Pack Mode       | 3-117  |

| 3-9    | Buffer Register Status During Read Pack             | 3-129  |

| 3-10   | EBCDIC-BCDIC Conversion (62 Set)                    | 3-133  |

| 3-11   | Sigma BCD-EBCDIC Conversion Chart                   | 3-134  |

| 3-12   | S and U Chassis Glossary of Terms                   | 3-136  |

| 3-13   | Y and Z Chassis Glossary of Terms                   | 3-138  |

| 3-14   | V and W Chassis Glossary of Terms                   | 3-143  |

| 4-1    | Tools and Test Equipment                            | 4-1    |

| 4-2    | Cleaning Equipment                                  | 4-1    |

| 4-3    | Station Interconnecting Cables                      | 4-5    |

| 4-4    | Visual Inspection Information                       | 4-6    |

| 4-5    | Preventive Maintenance Schedule                     | 4-8    |

| 4-6    | Tektronix Oscilloscope Control Designations         | 4-10   |

| 4-7    | Rewind One-Shot Adjustments                         | 4-14   |

### LIST OF TABLES (Cont.)

| Table | Title                                                     | Page |

|-------|-----------------------------------------------------------|------|

| 4-8   | Delay Counter Access                                      | 4-18 |

| 4-9   | Address Selection                                         | 4-19 |

| 4-10  | Station Connect Test                                      | 4-19 |

| 4-11  | Read and Write Amplifier Access Pins                      | 4-21 |

| 4-12  | Dockow Access Pins                                        | 4-22 |

| 4-13  | Write Dashaw Switches                                     | 4-23 |

| 4-14  | Ending Delay Logic Terms                                  | 4-23 |

| 4-15  | PET Data Patterns                                         | 4-29 |

| 4-16  | DET Eunctions                                             | 4-29 |

| 4-17  | Overlay Indicators                                        | 4-30 |

| 4-18  | Magnetic Tane System                                      | 4-40 |

| 4-19  | Magnetic Tape Transport Assembly, Replaceable Parts       | 4-43 |

| 4-20  | Photosense Assembly, Replaceable Parts                    | 4-47 |

| 4-21  | Capstan Motor Assembly, Replaceable Parts                 | 4-51 |

| 4-22  | Pool Motor Brake Assembly                                 | 4-55 |

| 4-23  | Auxiliary Control Panel Assembly, Replaceable Parts       | 4-56 |

| 4-24  | Tachometer Assembly Replaceable Parts                     | 4-57 |

| 4-25  | Fixed Vacuum Chamber Assembly, Replaceable Parts          | 4-58 |

| 4-26  | File Vacuum Chamber Assembly, Replaceable Parts           | 4-58 |

| 4-27  | Blower Shelf Assembly Replaceable Parts                   | 4-59 |

| 4-28  | Operator Control Panel Assembly, Replaceable Parts        | 4-62 |

| 4-29  | 29. Cabinat Assembly Replaceable Parts                    | 4-65 |

| 4-30  | Power Distribution Chassis Assembly, Replaceable Parts    | 4-65 |

| 4-31  | Relay Chassis Assembly, Replaceable Parts                 | 4-69 |

| 4-32  | Transport Drive Electronics Assembly, Replaceable Parts   | 4-73 |

| 4-33  | Forced Convection Heatsink Assembly, Replaceable Parts    | 4-77 |

| 4-34  | Rectifier Heatsink Assembly                               | 4-77 |

| 4-35  | Swing Frame Assembly, Replaceable Parts                   | 4-78 |

| 4-36  | Station Electronics Assembly, Replaceable Parts           | 4-78 |

| 4-37  | Station Electronics Chassis S Assembly, Replaceable Parts | 4-79 |

| 4-38  | Station Electronics Chassis U Assembly, Replaceable Parts | 4-80 |

| 4-39  | Controller Electronics Assembly, Replaceable Parts        | 4-81 |

| 4-40  | Controller Chassis V Assembly, Replaceable Parts          | 4-81 |

| 4-41  | Controller Chassis W Assembly, Replaceable Parts          | 4-82 |

| 4-42  | Controller Chassis Y Assembly, Replaceable Parts          | 4-83 |

| 4-43  | Controller Chassis Z Assembly, Replaceable Parts          | 4-84 |

| 4-44  | Front Door Assembly, Replaceable Parts                    | 4-84 |

| 4-45  | Manufacturer Code Index                                   | 4-85 |

### LIST OF RELATED PUBLICATIONS

The following publications contain information not included in this manual, but necessary for a complete understanding of the Magnetic Tape System Model 7371/7372/7374.

| Publication Title                                                                                       | Publication No. |

|---------------------------------------------------------------------------------------------------------|-----------------|

| Power Supply Model PT16 Technical Manual                                                                | 901080          |

| Power Supply Model PT18 Technical Manual                                                                | 900866          |

| Power Supply Model PT19 Technical Manual                                                                | 900867          |

| Peripheral Equipment Tester Model 7901<br>Technical Manual                                              | 901004          |

| Sigma Computer Systems Interface Design Manual                                                          | 900973          |

| SDS Sigma 2 Computer Reference Manual                                                                   | 900964          |

| SDS Sigma 5 Computer Reference Manual                                                                   | 900959          |

| SDS Sigma 7 Computer Reference Manual                                                                   | 900950          |

| SDS Sigma 2 Computer Technical Manual                                                                   | 900630          |

| SDS Sigma 5 Computer Technical Manual                                                                   | 901172          |

| SDS Sigma 7 Computer Technical Manual                                                                   | 901060          |

| Sigma 5 and 7 Magnetic Tape Test (7–Channel)<br>Diagnostic Program Manual                               | 901165          |

| Sigma 2 Magnetic Tape Test (7–Channel)<br>Diagnostic Program Manual                                     | 901536          |

| 7–Track Magnetic Tape Systems Models<br>7361/7362/7371/7372 Reference Manual<br>for SDS Sigma Computers | 900978          |

| Diagnostic Control Program for Sigma 5 and<br>Sigma 7 Computer Peripheral Devices Reference<br>Manual   | 900712          |

### SECTION I

### GENERAL DESCRIPTION

### 1-1 INTRODUCTION

### 1-2 SCOPE OF MANUAL

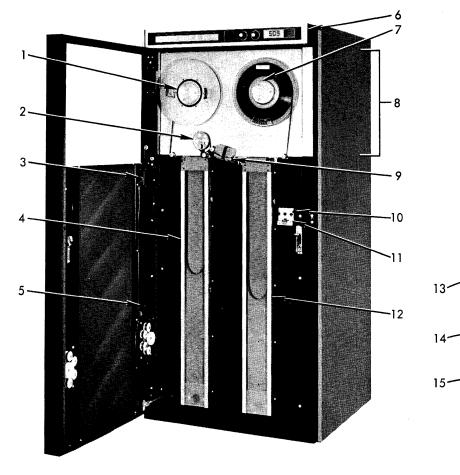

This publication describes the Magnetic Tape System Model 7371/7372/7374 (figures 1–1 and 1–2), designed and manufactured by Scientific Data Systems for use with Sigmaseries computers.

#### 1-3 RELATED PUBLICATIONS

The publications listed in the front matter contain information necessary for a complete understanding of the magnetic tape system.

#### 1-4 PURPOSE AND BRIEF DESCRIPTION

The magnetic tape system provides medium-speed (75 ips) input/output facilities for SDS Sigma-series computers. It may be used for program storage, as inputs to sorts and merges, for large data processing files, or as scratch or working tapes. Data is written and read in IBM-compatible tape format. The magnetic tape system records data on and reads data from standard 1/2-inch, seven-channel magnetic tape having a recording density of 200, 556, or 800 bits per inch. Binary and decimal (BCD) are the two standard read and write modes of operation for the model 7371/7372; packed binary reading and writing is an optional feature (model 7374).

The basic magnetic tape system is made up of the Magnetic Tape Controller Model 7371 and the Magnetic Tape Station Model 7372. A more extensive system may be formed by interconnecting up to eight magnetic tape stations, with complete control of the system originating from the magnetic tape station that contains the magnetic tape controller. In this manual, the 7371 magnetic tape controller will be referred to as "the magnetic tape controller" or "the controller"; the 7372 magnetic tape station will be identified as "the magnetic tape station" or "the station."

### 1-5 PHYSICAL DESCRIPTION

### 1-6 GENERAL

The basic magnetic tape system is contained in a standard Sigma cabinet 63-1/2 inches high, 29-1/4 inches wide, and 35 inches deep, having front and rear access. The tape transport mechanism is mounted at the front of the cabinet. Access to the tape handling portion is provided through a sliding glass door. A swing frame at the rear of the cabinet holds the two chassis of station electronics (S and U) and

the four additional chassis (V, W, Y, and Z) that comprise the magnetic tape controller. (See figures 1-1 and 1-2.)

When more than one station is used in the system, they are bolted together, side by side, and side panels are provided for the two outside ends only. The station containing the controller is located nearest the center of the system. The weight of a magnetic station alone is approximately 850 pounds; the weight of the basic system (magnetic tape station with controller) is approximately 950 pounds.

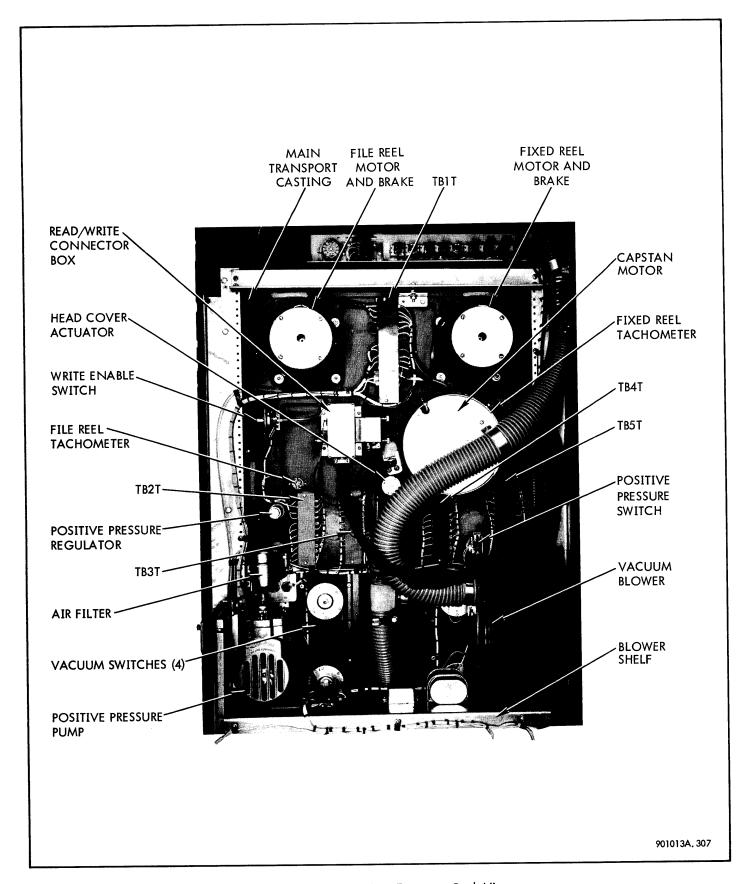

1-7 MAGNETIC TAPE STATION (See figures 1-1, 1-2, and 3-6)

The station consists of the main components described in paragraphs 1-8 through 1-17.

### 1-8 Transport Assembly

The transport assembly is mounted on the top front portion of the station. It includes the following:

- a. Main transport casting on which the transport components are mounted (figure 1-2)

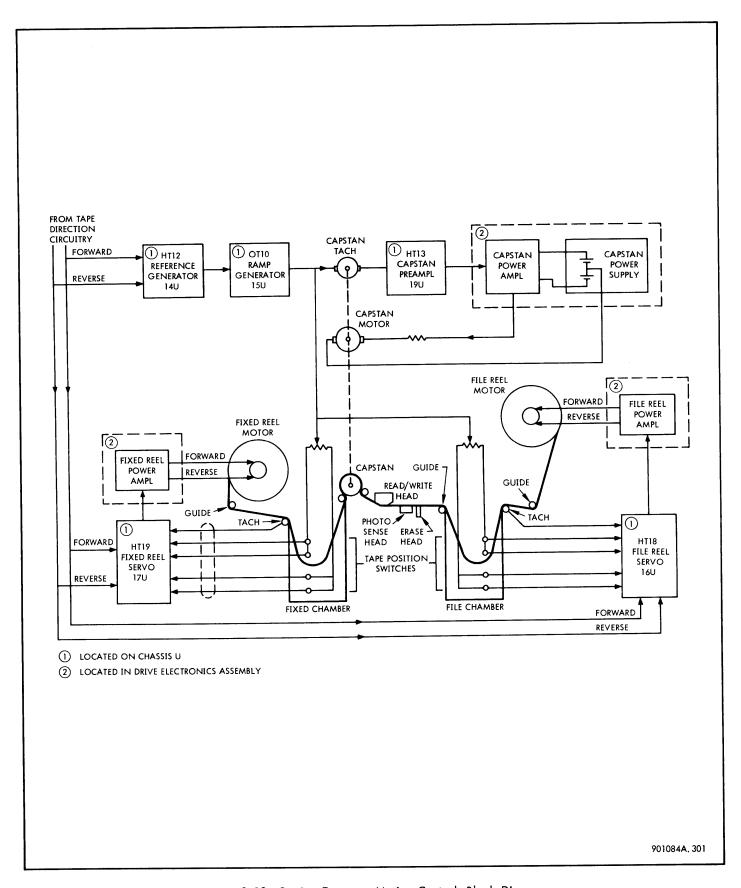

- b. Reel hub assemblies, reel motors, and reel tachometers (figure 3-6)

- c. Tape drive capstan, capstan motor, and tachometer (figure 1-1)

- d. Read/write head assembly (includes tape cleaner) (figure 1-1)

- e. Tape guides (figure 4-11)

- f. Photosense assembly (figure 4–11)

- g. Write enable switch (figure 1-2)

- h. Magnetic head cover actuator (figure 1-2)

- i. Positive pressure switch (figure 3-10)

- i. Swinging door interlock switch (figure 1-1)

- k. Auxiliary control panel (figure 1-1)

Figure 1-1. Magnetic Tape System Model 7371/7372/7374, Front and Side Views

FRONT VIEW

- 1. FIXED REEL HUB

- 2. CAPSTAN AND TACHOMETER

- 3. TOP DOOR SWITCH

- 4. FIXED TAPE STORAGE VACUUM CHAMBER

- 5. BOTTOM DOOR SWITCH

- 6. OPERATOR CONTROL PANEL

- 7. FILE REEL HUB

- 8. STATION TRANSPORT

- 9. READ/WRITE HEAD ASSEMBLY

- 10. SWINGING DOOR INTERLOCK

- 11. AUXILLARY CONTROL PANEL

- 12. FILE TAPE STORAGE VACUUM CHAMBER 18. CONTROLLER MODEL 7371

### SIDE VIEW

- 13. BLOWER SHELF

- 14. TRANSPORT DRIVE ELECTRONICS

- 15. POWER SUPPLY PT19

- 16. RELAY CHASSIS

- 17. STATION ELECTRONICS

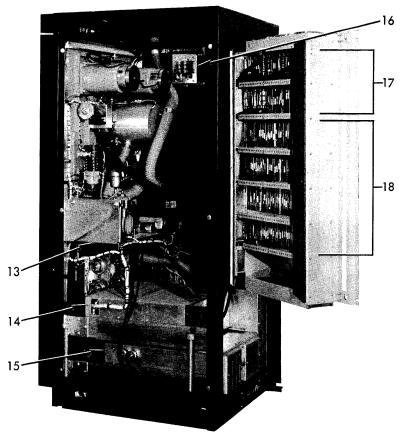

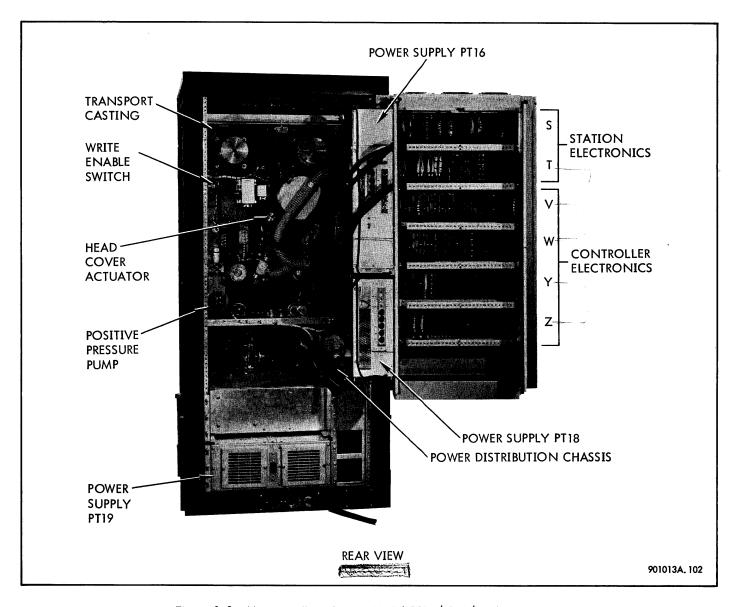

Figure 1-2. Magnetic Tape System Model 7371/7372/7374, Rear View

### 1-9 Operator Control Panel (Figure 1-1)

The operator control panel is mounted on the front of the station above the station transport main casting. The panel consists of switches for operating the station and lamp indicators for displaying the current status and condition of the station. It provides the necessary control signals for address selection, loading, unloading, and rewinding, as well as the signals needed for switching the station on-line or off-line.

### 1-10 Vacuum System

The vacuum system includes the following:

- a. Vacuum blower (figure 3-6)

- b. Tape storage chambers (figure 1-1)

- c. Vacuum switches (Figure 3-6)

- d. Vacuum plenum (located at bottom front of station)

### 1-11 Positive Pressure System (Figure 1-2)

Positive air pressure is generated by the positive pressure pump and is fed to the air plenum in the main casting. The plenum supplies air to the tape guides and operating pressure for the head door actuator and positive pressure interlock.

### 1-12 Blower Shelf Assembly (Figure 1-1)

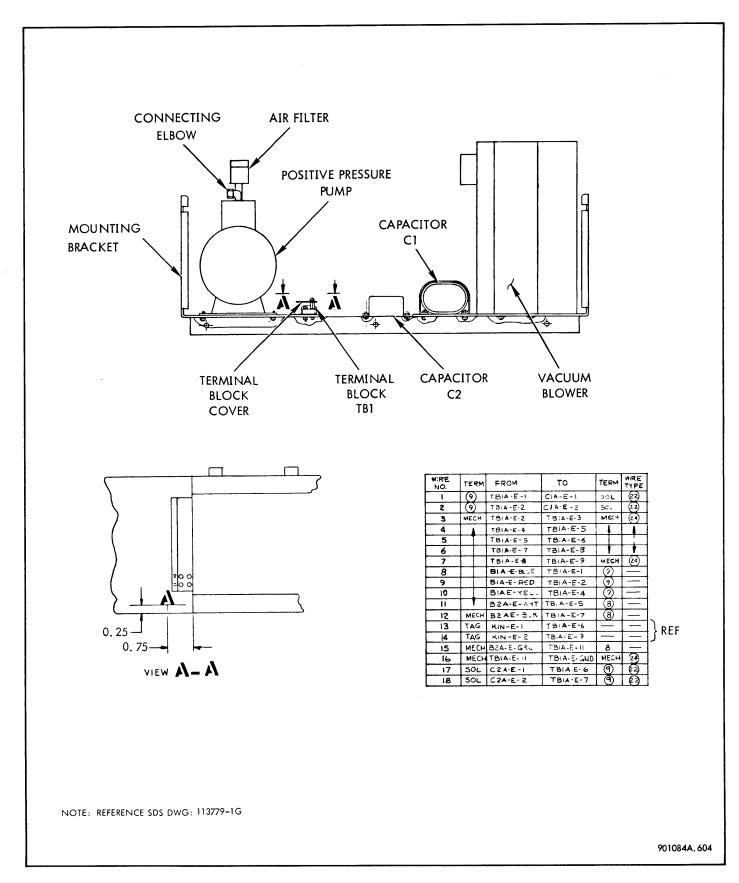

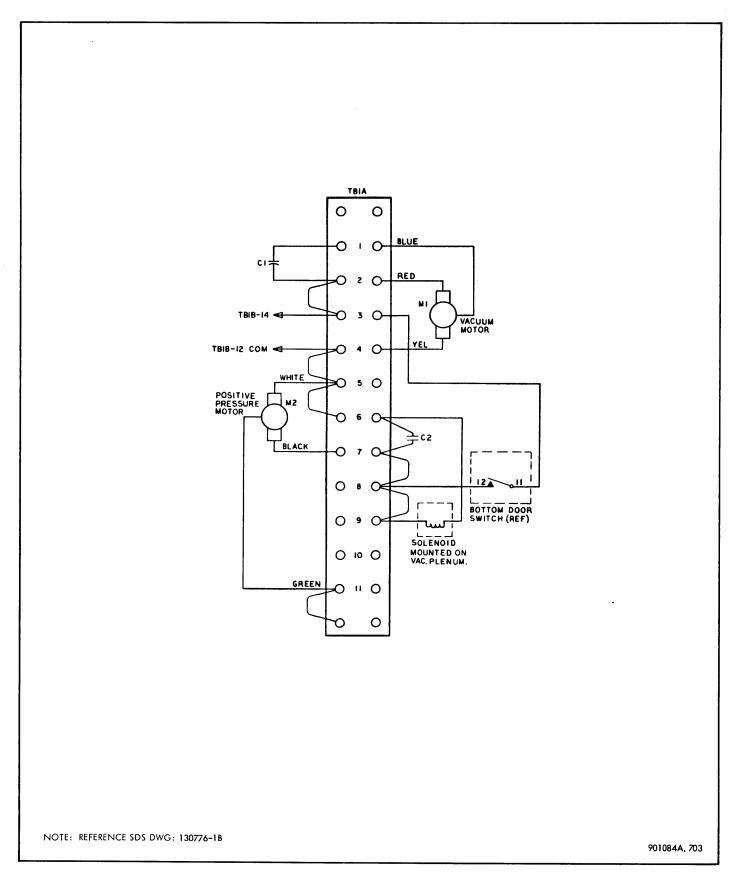

The blower shelf assembly is mounted at the front center portion of the station behind the tape vacuum chambers. Mounted on the blower shelf assembly are the positive pressure pump and the vacuum blower.

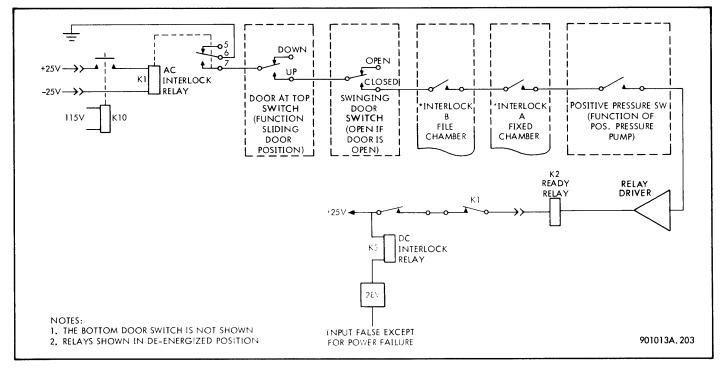

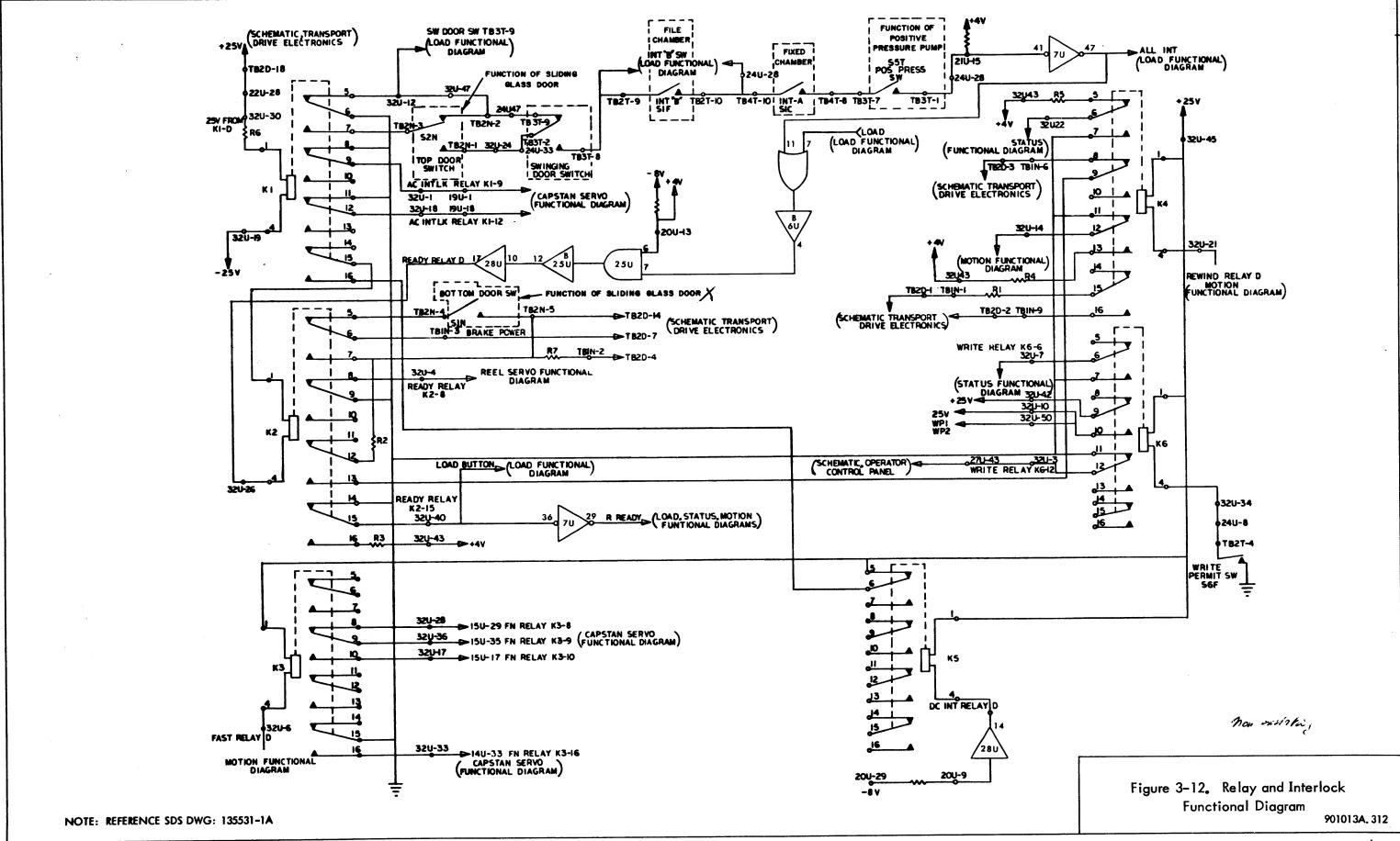

### 1-13 Relay Chassis Assembly (Figures 1-1 and 4-25)

The relay chassis assembly is mounted at the top left center side of the main frame. It contains the ac interlock, ready, speed, rewind, dc interlock, and file protect relays.

### 1-14 Power Supplies (Figure 1-1)

There are three power supplies: PT19, PT18, and PT16. Power supply PT19 is located at the bottom rear of the station. It generates the 2000 Hz power that is used as input for both the PT16 and PT18 supplies. The PT18 supply is mounted on the bottom left-hand side of the swinging frame assembly. This supply generates +25 Vdc and -25 Vdc voltages. The PT16 supply is mounted at the top left-hand side of the swinging frame assembly. This supply generates +4 Vdc, +8 Vdc, and -8 Vdc voltages.

### 1-15 Power Distribution Chassis (Figure 1-2)

The power distribution chassis is mounted near the bottom front left-hand corner of the station. It provides necessary ac power controls to properly operate the station and devices connected in the system.

### 1-16 Transport Drive Electronics (Figure 1-2)

The transport drive electronics contains power supplies and power amplifiers for driving the capstan motor and the reel motor. It is contained in one assembly mounted near the bottom rear of the station cabinet, behind the tape vacuum chamber and below the motors.

### 1-17 Station Electronics (Figure 1-2)

The station electronics are mounted in module chassis S and U on the swinging frame assembly. Chassis S includes the modules that contain circuitry to handle the station data operations. Chassis U includes the modules that contain circuitry for control of the station motion operations.

### 1-18 MAGNETIC TAPE CONTROLLER (Figure 1-2)

The controller is comprised of module chassis V, W, Y, and Z. Chassis V and W enclose the modules which contain circuitry for handling the system data operations. The modules which contain circuitry for control of the system motion operations are included in chassis Y and Z.

### 1-19 FUNCTIONAL DESCRIPTION

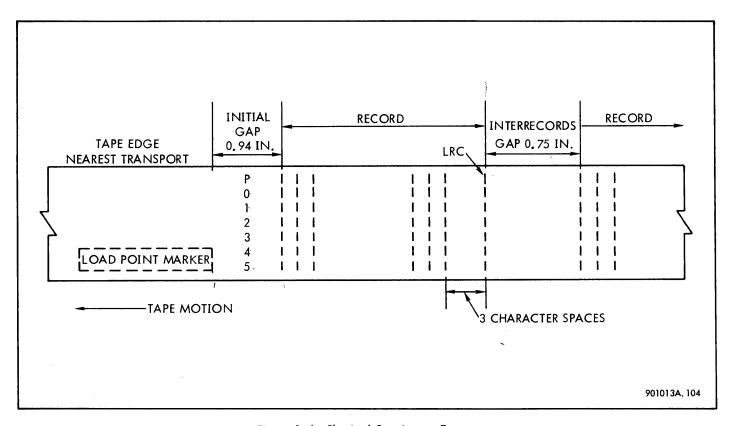

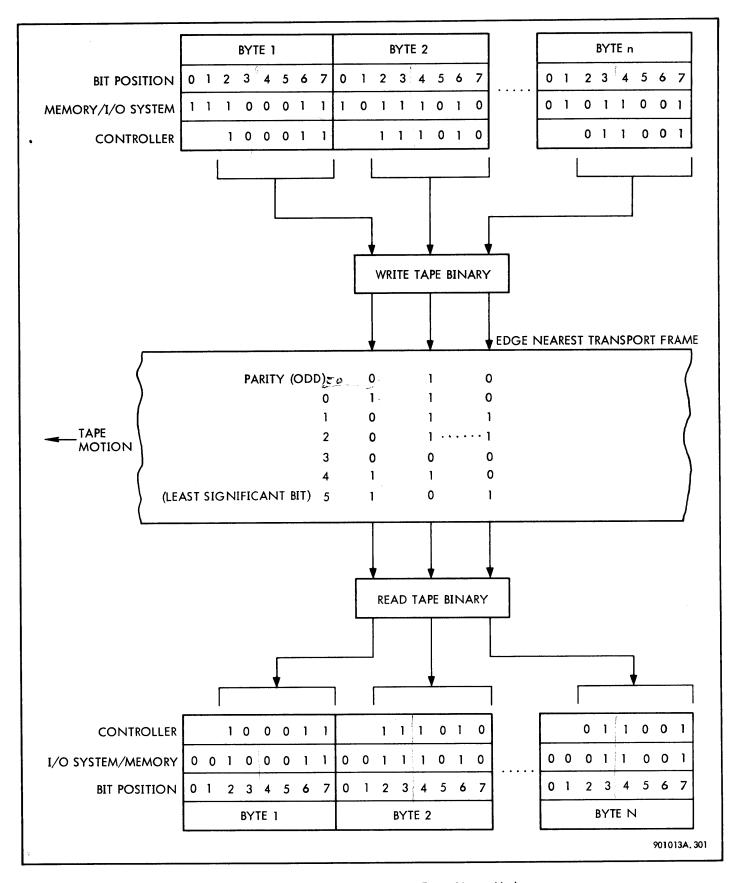

The magnetic tape system communicates with the computer through the input/output processor (IOP), which controls tape system operation. It may store data on the magnetic tape (write operation) or retrieve it (read operation). The information is recorded on seven parallel tracks along the length of the tape at a selectable density of 200, 556, or 800 bytes per inch. Each byte consists of seven bits (six data bits plus one parity bit), which form a row across the width of the tape. (See figure 1-4.) The bits are formed

by the nonreturn to zero, change on ones recording method (NRZ1). In this method, the write head current causes the state of flux in the tape to be switched from one level of saturation to the opposite level each time a binary one is recorded. The absence of such a change represents a binary zero.

### 1-20 MAGNETIC TAPE STATION

The tape transport moves the tape across a read/write head in response to commands from the computer or signals generated from the operator control panel. In a write operation, the data electronics translates the information from the tape controller and drives the write head to record the data on the tape. In a read operation, the information detected by the read head is amplified and then transferred to the controller.

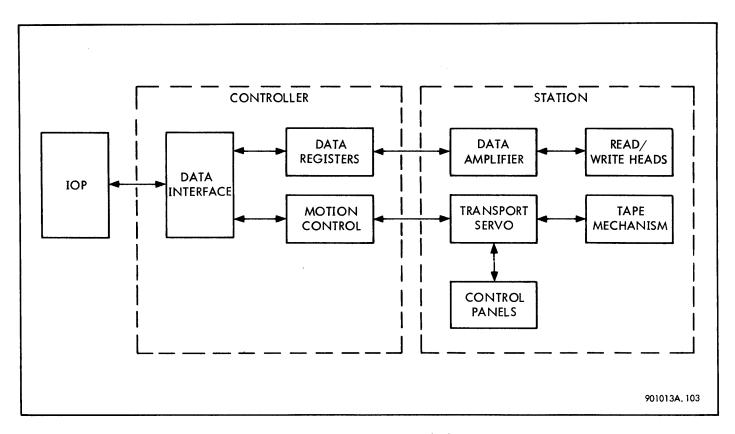

### 1-21 MAGNETIC TAPE CONTROLLER

In automatic operation, all operating commands and read/write data transfers for the tape station are handled by the magnetic tape controller. Data to be recorded is received from the computer through the IOP and is routed to the magnetic tape controller and then to the selected tape station. The data flow follows a reverse sequence during a read operation. Refer to figure 1-3 for an overall functional block diagram of the magnetic tape system.

### 1-22 TAPE FORMAT

The tape data format conforms to IBM 729, seven-track format (see figure 1-4). Information on tape is arranged in records. Each record may contain any number of bytes, limited only by the length of the usable portion of tape.

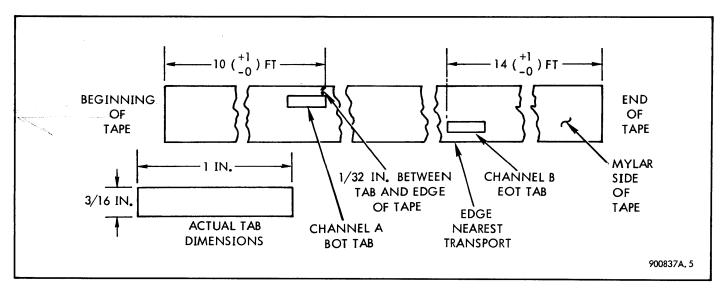

Records are separated on tape by an interrecord gap of approximately 0.750 inches. When a write operation is initiated from the load point, a gap of approximately 0.94 inches in length is automatically inserted between the beginning of tape (BOT) marker and the first record. At the end of each record three blank characters are written, followed by a longitudinal redundancy check character mark (LRC). A group of one or more consecutive records forms a file of information. Adjacent files are separated by a tape mark record, which consists of a single byte. An LRC character occurs three spaces after the tape mark.

### 1-23 SPECIFICATIONS AND LEADING PARTICULARS

### 1-24 GENERAL REQUIREMENTS

Tables 1-1 and 1-2 list the general requirements and specifications for the magnetic tape system.

Figure 1-3. Magnetic Tape System Block Diagram

Figure 1-4. Physical Spacing on Tape

Paragraph 1-25 SDS 901013

Table 1-1. General Requirements

| Characteristics            | Specifications                                   |

|----------------------------|--------------------------------------------------|

| Power requirements         |                                                  |

| Primary                    | 108–127 Vac, 30A<br>45–66 Hz, 1Ø*                |

| Secondary                  | ±25 Vdc (±10%)<br>±8 Vdc (±10%)<br>+4 Vdc (±10%) |

| Environmental requirements |                                                  |

| Temperature range          | 50°F-140°F                                       |

| Humidity range             | 5% - 80%                                         |

| Logic levels               |                                                  |

| True                       | +4.0 ±0.4 Vdc                                    |

| False                      | +0 <b>.</b> 25 ±0 <b>.</b> 25 Vdc                |

| Tape characteristics       |                                                  |

| Recording density          | 200, 556, or 800 bpi                             |

| Width                      | 1/2 in.                                          |

| Туре                       | 1.5 mil base, Mylar                              |

| Reel size                  | 10.5 in. diameter<br>3.688 in. hub (IBM)         |

$<sup>^{\</sup>star}$  50 Hz operation requires the 50 Hz modification kit part No. 137746

Table 1-2. Parameter Definitions and Specifications

| Parameter         | Definition                                                                                                                     | Specification   |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Start<br>time     | The time interval between the receipt of a start command and the attainment of a tape speed that is within 8% of nominal speed | 5.0 ms max      |

| Start<br>distance | The distance traversed by a point on the tape during the start time                                                            | 0.190 ±0.01 in. |

Table 1–2. Parameter Definitions and Specifications (Cont.)

| Parameter                   | Definition                                                                                                                                       | Specification   |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Nominal<br>tape<br>speed    | The speed at which the tape<br>moves across the read/write<br>heads for purposes of reading<br>and writing                                       | 75 ips          |

| Total<br>speed<br>variation | The maximum deviation from<br>the nominal tape speed at any<br>time after start time and pre-<br>vious to a stop command                         | ±8%             |

| Fast<br>tape<br>speed       | The speed at which the tape<br>moves for purposes other than<br>reading and writing                                                              | 250 ips ±5%     |

| Stop<br>time                | The time interval between the receipt of a stop command and the cessation of tape motion                                                         | 5.0 ms max      |

| Stop<br>distance            | The distance traversed by a point on the tape during the stop time                                                                               | 0.190 ±0.01 in. |

| Skew                        | The displacement of a bit from<br>a line across the tape drawn<br>perpendicular to the direction<br>of ideal tape motion at the<br>head assembly |                 |

| Static<br>skew              | The nonvarying portion of skew contributed by the mechanical tolerances of the tape, transport, and head assembly                                | 225 µin max     |

| Dynamic<br>skew             | The portion of skew contributed by time-variant tape motion not parallel to the ideal tape path                                                  | 225 µin (p-p)   |

### 1-25 FUSE AND LAMP COMPLEMENT

The fuses and lamps used in the magnetic tape system are listed and described in table 2-1. Refer to table 4-28 for lamp location and identification.

# SECTION II OPERATION AND PROGRAMMING

### 2-1 CONTROLS AND INDICATORS

The following information defines the operation and function of all the controls and indicators in the station.

Manual control of the tape station is provided by switches located in one of the following:

- a. Operator control panel

- b. Auxiliary control panel

- c. Interlock system

- d. Power distribution chassis

- e. Power supply PT19 and PT16 chassis

All indicators are contained on the operator control panel. They display the current status and conditions of the tape system.

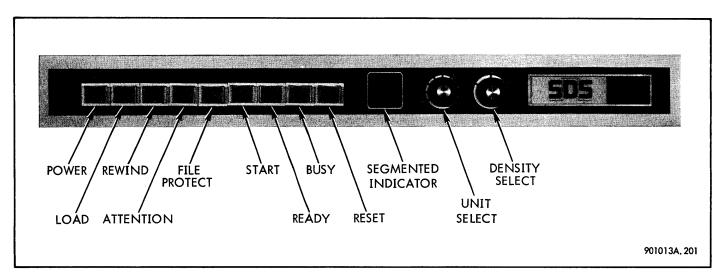

# 2-2 OPERATOR CONTROL PANEL SWITCHES (See figure 2-1)

During normal operation, the only controls accessible to the operator are those on the control panel. This panel is mounted on the front of the tape station, above the transport main casting. The names, reference designators, types, and functions of the control switches are listed in table 2-1.

### 2-3 AUXILIARY (MAINTENANCE) CONTROL PANEL SWITCHES (See figure 1-1)

The auxiliary control panel is inset directly below the lower right-hand corner of the station transport main casting. It is accessible from the front of the station when the swinging front door is open. The panel is equipped with three switches, labeled FORWARD, REVERSE, and FAST. The switches are used for motion control of the station transport when the station is being operated in the manual mode.

The FORWARD and REVERSE switches are used to control tape directional motion at a speed of 75 ips. For fast tape motion, the direction switch selected is used in conjunction with the FAST switch, which causes the fast tape speed circuitry to be energized, producing a 250 ips tape movement.

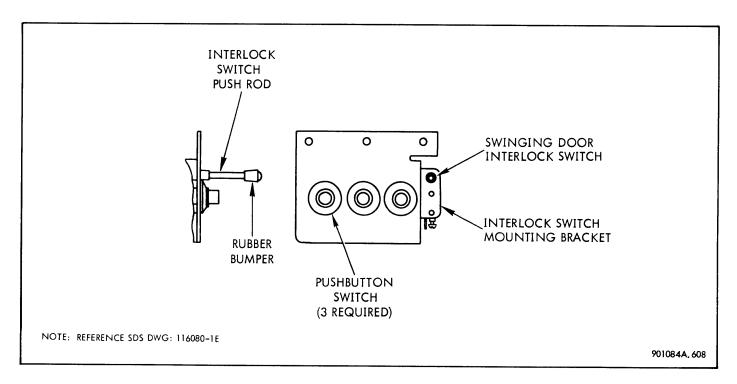

### 2-4 SWINGING FRONT DOOR INTERLOCK SWITCH

The swinging door interlock switch is a part of the auxiliary control panel. Since this switch is in the door interlock system, the door must be closed for the station to become ready. The switch may be actuated with the door open for maintenance purposes by pulling outward on the pushrod. Under normal operating conditions, the switch opens when the swinging door is swung outward and closes when the swinging door is shut. Table 2-2 lists the auxiliary panel switches and their functions.

Figure 2-1. Operator Control Panel, Front View

Table 2–1. Operator Control Panel Switches and Indicators

| Name      | Reference<br>Designator | Туре                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|-------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER     |                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Switch    | \$1                     | Dpdt, alternate action pushbutton switch  | Controls the primary power to the drive electronics and to the motors and blowers in the positive pressure and vacuum systems. It is effective only if the circuit breaker (CB1) is closed on the power distribution chassis                                                                                                                                                                                                                                                                                                              |

| Indicator | DS1                     | Incandescent 28-Vdc<br>midget lamp        | Lights when the circuit breaker on the power distribution chassis is set to ON and the POWER switch is pressed on the operator control panel                                                                                                                                                                                                                                                                                                                                                                                              |

| LOAD      |                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Switch    | S2                      | Dpdt, momentary contact pushbutton switch | Causes the transport to load tape automatically into the vacuum chambers. Actuation of this switch feeds tape from the file reel into both the file and fixed vacuum chambers. The tape is then driven to the load point (BOT marker), at which time the tape motion ceases and the unit becomes ready. The switch is pressed after loading a new tape onto the file reel. When the BOT marker is detected, the LOAD indicator lights on the operator control panel                                                                       |

| Indicator | DS2                     | Incandescent 28–Vdc<br>midget lamp        | Lights whenever the tape reaches the load point position. This position is reached with tape motion stopped and the beginning of tape reflective marker (BOT) positioned directly under the photosense head                                                                                                                                                                                                                                                                                                                               |

| REWIND    |                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Switch    | S3                      | Dpdt, momentary contact pushbutton switch | Initiates an off-line rewind operation, provided the station is not in the automatic mode. When this switch is activated, fast reverse tape motion takes place and the tape rewinds until the BOT marker is detected, at which point tape motion ceases and the LOAD indicator lights on the operator control panel. When this switch is pressed, with the tape in the load point position, an unload operation is initiated. The unload operation is performed to unwind the portion of tape ahead of the BOT marker from the fixed reel |

| Indicator | DS3                     | Incandescent 28–Vdc<br>midget lamp        | Lights throughout the duration of a rewind operation. It goes out when the beginning of the tape marker is detected by the photosense head. It also lights when fast tape motion is initiated from the auxiliary (maintenance) panel                                                                                                                                                                                                                                                                                                      |

| ATTENTION |                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Switch    | S4                      | Dpdt, momentary contact pushbutton switch | Pressing this switch when the station is not in automatic sets a latch that provides a device interrupt to the processor when the station is switched into automatic. Pressing this switch when the station is in automatic has no effect                                                                                                                                                                                                                                                                                                 |

| Indicator | DS4                     | Incandescent 28–Vdc<br>midget lamp        | Lights when the ATTENTION switch is pressed while the station is not in the automatic mode. It remains on until the interrupt call signal comes true from the controller                                                                                                                                                                                                                                                                                                                                                                  |

|           |                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

(Continued)

### SDS 901013

Table 2-1. Operator Control Panel Switches and Indicators (Cont.)

| Name         | Reference<br>Designator | Туре                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|-------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FILE PROTECT |                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

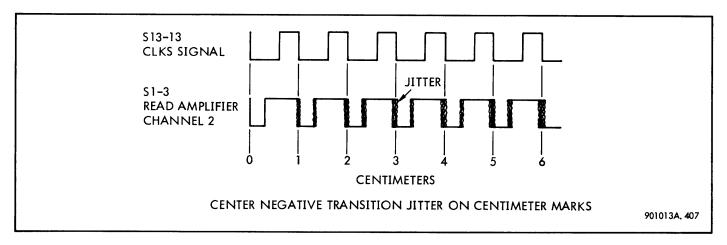

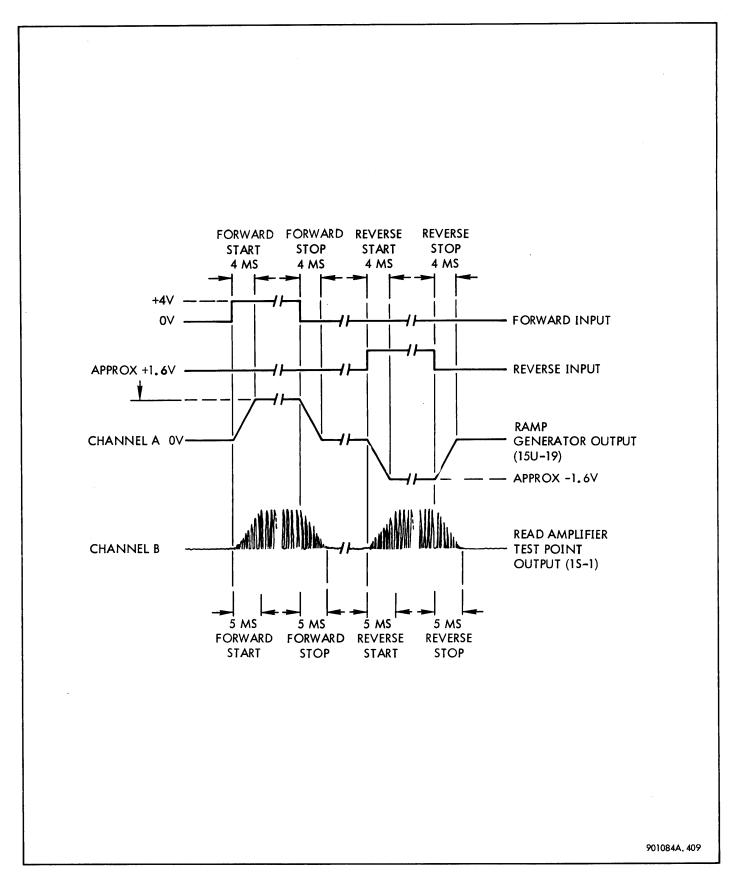

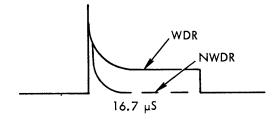

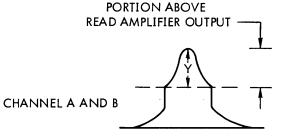

| Indicator    | DS5                     | Incandescent 28–Vdc<br>midget lamp        | Lights when the write enable ring is not installed in the file reel. This constitutes a file protect condition. No writing can take place under these circumstances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |